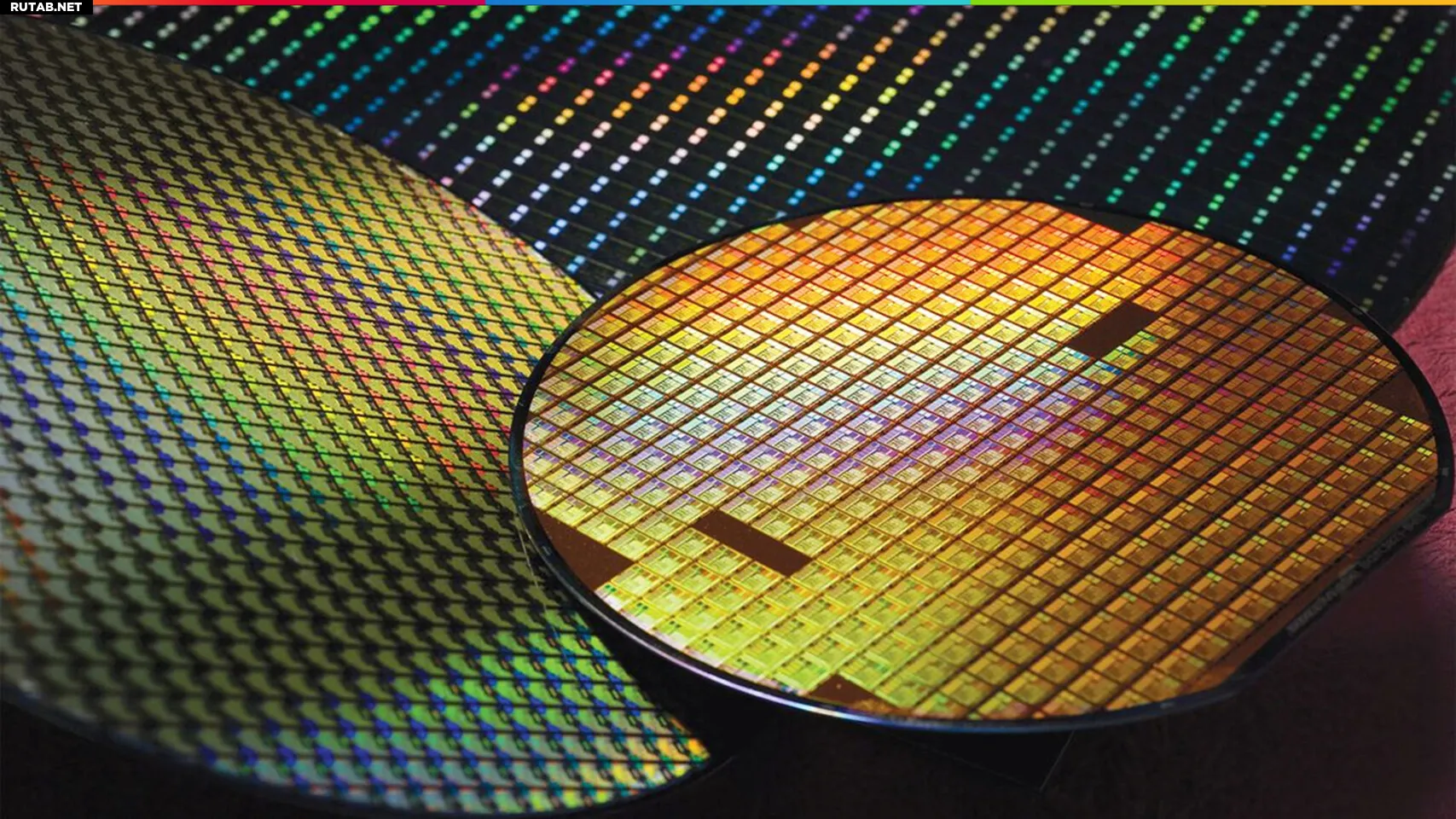

Cadence и TSMC расширяют сотрудничество в области ИИ для проектирования чипов нового поколения

Компания Cadence объявила о значительных успехах в области автоматизации проектирования чипов и разработки IP-блоков, достигнутых благодаря углублению партнерства с TSMC. Цель сотрудничества — создание передовой проектной инфраструктуры для ускорения вывода на рынок решений для искусственного интеллекта и высокопроизводительных вычислений (HPC).

Компании тесно работают над широким спектром технологий — от ИИ-управляемых систем автоматизированного проектирования (EDA) до 3D-чипов, IP-блоков и фотоники. Совместные разработки уже сейчас используются для создания самых передовых полупроводников в мире.

Инфраструктура проектирования была адаптирована для передовых технологических процессов TSMC, включая N3, N2 и A16. ИИ-методологии Cadence для проектирования чипов и 3D-IC теперь доступны для этих процессов, а также для новых возможностей платформы TSMC 3DFabric. Кроме того, ведется совместная работа над EDA-инструментами для будущего процесса A14, первый комплект для проектирования (PDK) для которого ожидается в конце этого года. Также несколько новых IP-блоков от Cadence прошли апробацию на кремнии и доступны для технологии N3P.

«Cadence и TSMC по-прежнему стремятся ускорить и улучшить процесс проектирования передовых кремниевых решений для наших клиентов», — заявил Чин-Чи Тенг, старший вице-президент и генеральный менеджер группы Digital and Signoff Group в Cadence.

«TSMC вместе с партнерами по платформе Open Innovation Platform (OIP), такими как Cadence, решает некоторые из самых сложных задач в разработке полупроводников для повышения производительности и энергоэффективности ИИ-систем», — добавил Авик Саркар, директор подразделения по управлению экосистемой и альянсами в TSMC.

ИИ-решения для передовых процессов TSMC

Партнеры совместно разрабатывают ИИ-решения для проектирования, позволяющие достигать оптимальных показателей мощности, производительности и площади (PPA) на процессе N2. TSMC интегрировала в свои инструменты технологию Cadence JedAI и функции повышения производительности на базе ИИ-помощника Innovus+.

Повышение эффективности проектирования 3D-чипов

Решения Cadence для 3D-IC обеспечивают полную поддержку конфигураций advanced packaging и стекирования кристаллов, предлагаемых платформой 3DFabric. Последние инновации включают функции автоматизации для соединений, физической реализации и анализа нескольких чиплетов.

Передовые IP-блоки для TSMC N3P

Cadence продолжает внедрять инновации, предлагая проверенные на кремнии IP-решения для процесса N3P. В числе новинок — первый IP для HBM4 на N3P, высокоскоростные интерфейсы памяти LPDDR6/5X и DDR5, а также IP для PCIe 7.0 со скоростью 128 GT/s и 224G SerDes для ИИ-инфраструктуры.

Совместные усилия Cadence, TSMC и экосистемы OIP направлены на поддержку «суперцикла» ИИ, упрощая для клиентов путь от проекта до готового чипа.

0 комментариев