Sarcina Technology разработала новые интерконнекты UCIe-A/S для чиплетов

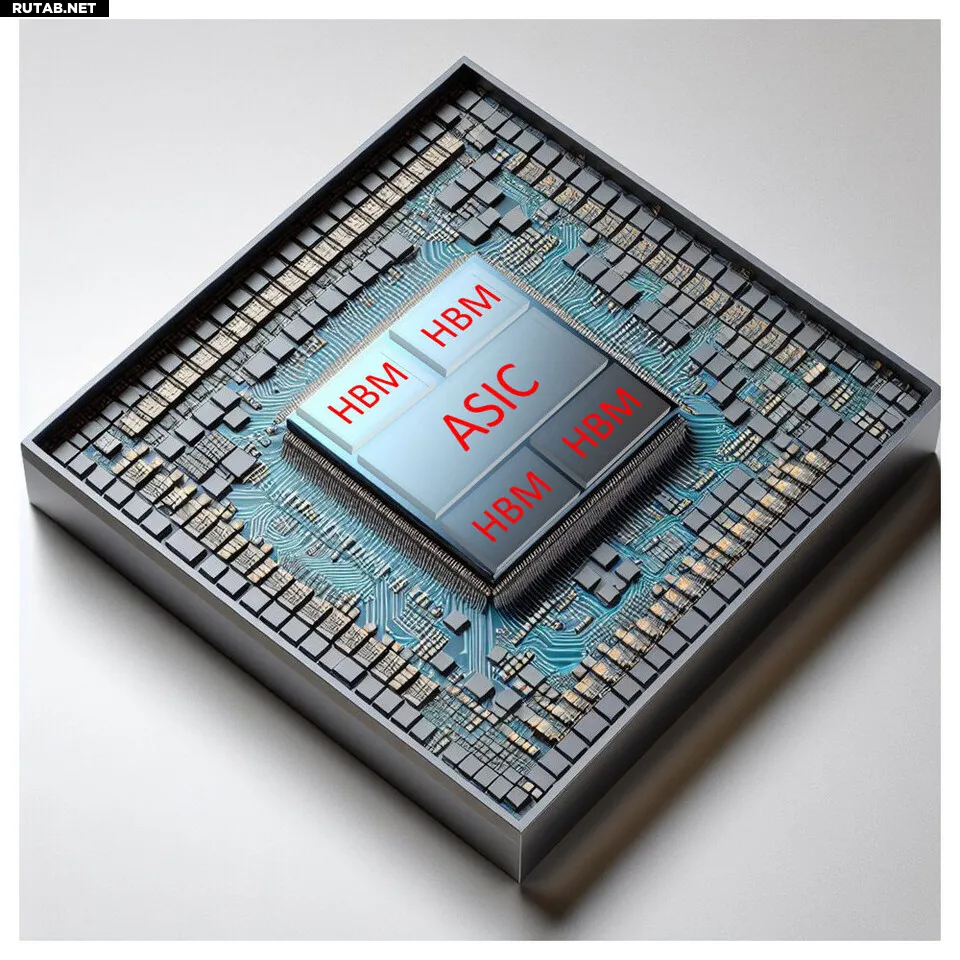

Компания Sarcina Technology, специализирующаяся на проектировании полупроводниковых и фотонных упаковок, объявила о разработке запатентованных методик для протоколов UCIe-A (Universal Chiplet Interconnect Express-Advanced) и UCIe-S (Standard). Новые решения включают оптимизированный дизайн интерпозера RDL (redistribution layer) для соединений кристалл-кристалл, поддерживающий скорость передачи данных до 32 гигабит в секунду (GT/s) при минимизации перекрестных помех и максимальной целостности сигнала.

По словам генерального директора Sarcina Technology Ларри Зу: «Одна из ключевых проблем, которую мы решаем, — это расположение соединительных проводов для минимизации перекрестных помех и повышения целостности сигнала. Учитывая ограничения доступного пространства и производственные ограничения, это сложная задача».

Протокол UCIe-A

Методология Sarcina для протокола UCIe-A обеспечивает:

- Скорость передачи данных 32 GT/s при полном соответствии спецификациям UCIe 2.0

- Оптимизированную архитектуру маршрутизации, значительно снижающую перекрестные помехи

- Максимальное использование 3D-пространства с маршрутными каналами, строго ограниченными краем кристалла

- Многомерную оптимизацию маршрутизации для данных, тактовых и резервных сигналов

- Экономически эффективные проекты, минимизирующие слои маршрутизации RDL

- Стандартизированные макеты RDL, повышающие выход годных изделий

Методологии UCIe-S

Решения UCIe-S предназначены для органических подложек и продвинутых PCB с технологией HDI и обеспечивают:

- Минимальные потери при вставке и перекрестные помехи

- Структурированную многослойную маршрутизацию в ультракомпактном 3D-пространстве

- Совместимость со связями упаковка-упаковка

- Проверенную производительность 32 GT/s

- Бесперебойную связь кристалл-кристалл без дополнительного энергопотребления

Комбинирование возможностей

Объединяя возможности UCIe-A и UCIe-S, Sarcina предоставляет комплексную платформу для проектирования и моделирования чиплетных интерконнектов, что позволяет клиентам:

- Разделять монолитные SoC на чиплеты для повышения выхода годных и снижения стоимости

- Интегрировать гетерогенные технологии на разных процессных узлах

- Включать кремниевые фотонные кристаллы и блоки волоконных массивов в упаковки Co-Packaged Optics

- Развертывать масштабируемые и производительные решения для AI-ускорения

Ларри Зу подчеркивает: «Мы не просто проектируем интерконнекты — мы помогаем заложить основу для систем искусственного интеллекта следующего поколения».

0 комментариев