TSMC готовится к переходу с CoWoS на CoPoS с панелями размером 750 × 620 мм

Компания TSMC, по сообщениям, готовится к переходу с технологии CoWoS на новую панельную упаковку под названием CoPoS (Chip-on-Panel-on-Substrate). Пилотные линии планируется запустить уже в 2026 году, а массовое производство должно начаться в период с конца 2028 года до первой половины 2029 года.

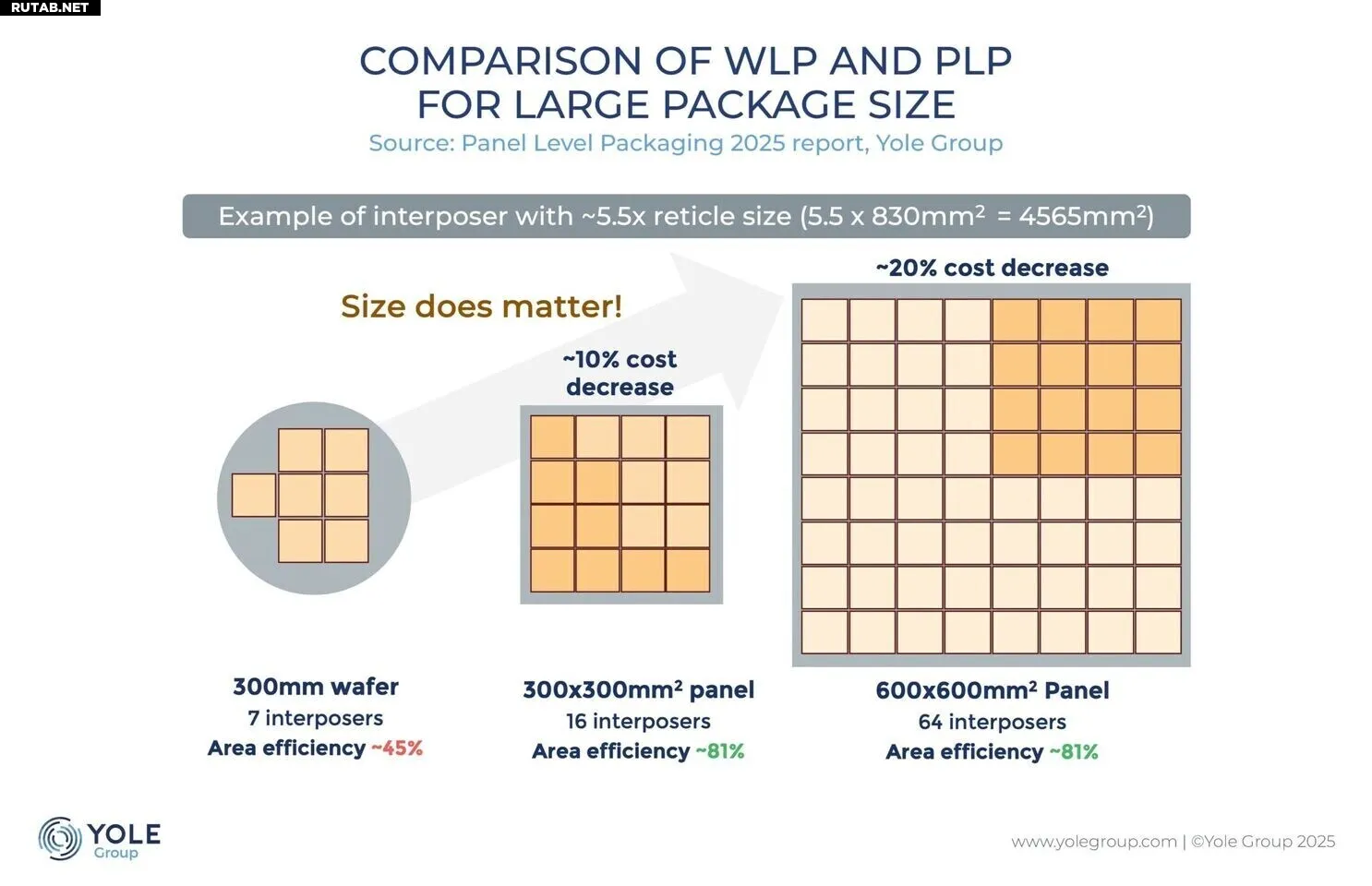

Новый подход предполагает замену 300-миллиметровых кремниевых интерпозеров на крупные квадратные и прямоугольные панели. Первоначальные форматы составят около 310 × 310 мм, а в дальнейшем появятся варианты размером 515 × 510 мм и даже 750 × 620 мм. Такой крупный формат позволит сократить потери площади по краям, использовать более крупные ретикли и маски для AI-ускорителей, а также упростит размещение большего количества чипов и памяти HBM в одном корпусе.

Технически CoPoS объединяет идеи CoWoS с упаковкой на уровне панелей (fan-out panel-level packaging), создавая слои RDL на стеклянных или сапфировых панелях вместо круглых кремниевых пластин. Разработка и производство CoPoS будут вестись на кампусе AP7 в Чиаи, где фазы 4 и 5 займутся панельными работами. Также TSMC планирует развернуть соответствующие мощности на будущих предприятиях в Аризоне.

Заказы на оборудование и инструменты уже размещаются, а среди поставщиков значатся такие глобальные компании, как KLA и Applied Materials, а также тайваньские производители, включая Innolux. Панельный подход обещает более высокую эффективность использования площади, снижение стоимости на один упакованный ускоритель и меньше проблем с деформацией при увеличении размеров корпусов. При этом TSMC продолжит поддерживать существующую линейку CoWoS в течение переходного периода.

Источник: DigiTimes

0 комментариев