TSMC разрабатывает новую технологию упаковки чипов CoPoS с размерами 310 × 310 мм

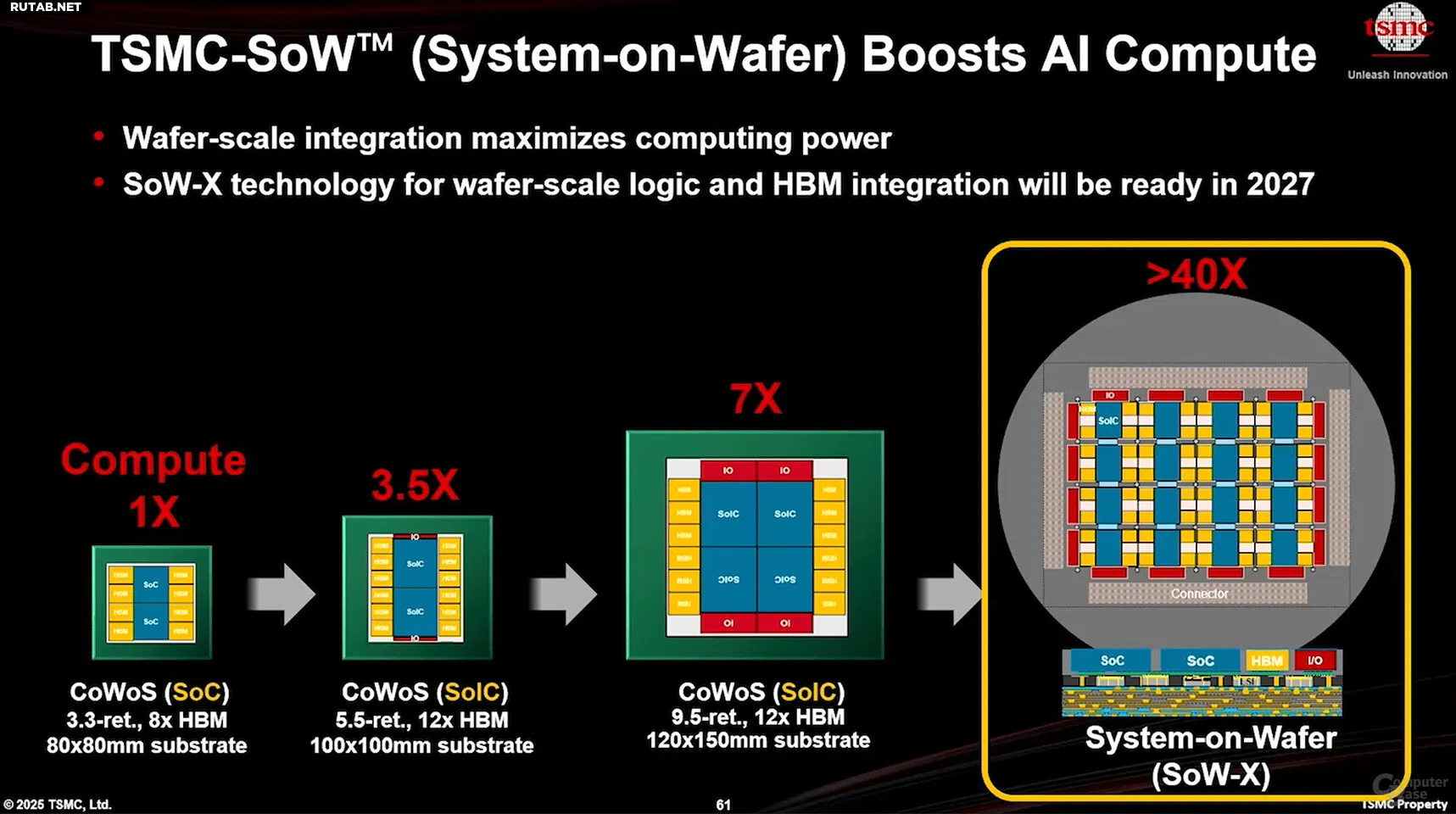

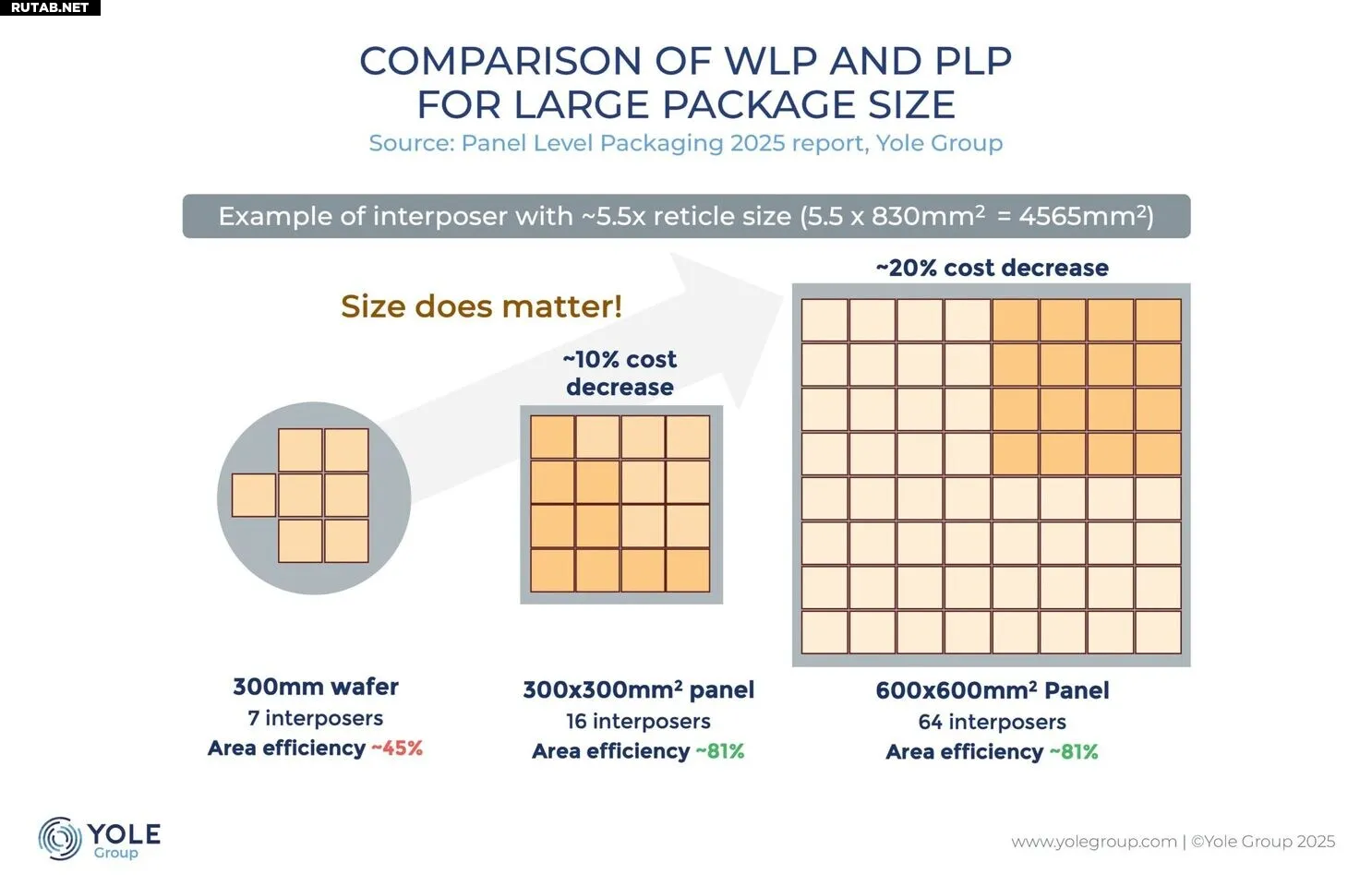

Компания TSMC анонсировала новую технологию упаковки чипов под названием CoPoS («Chips on Panel on Substrate»). В отличие от текущего стандарта CoWoS с размерами до 120 × 150 мм, новая технология позволит использовать прямоугольные панели размером 310 × 310 мм, что увеличит полезную площадь более чем в 5 раз.

CoPoS относится к технологии панельного уровня (PLP), которая обеспечивает более высокую пропускную способность и снижает стоимость производства по сравнению с упаковкой на уровне пластин (WLP). Это позволит интегрировать больше компонентов, включая чипы HBM4 и GPU, в единый корпус.

Пилотная линия CoPoS будет запущена в 2026 году на дочернем предприятии Visionchip. К 2027 году TSMC планирует доработать процесс, а массовое производство начнётся в конце 2028 — начале 2029 года на площадке Chiayi AP7. Ожидается, что NVIDIA станет первым партнёром, использующим CoPoS для своих GPU.

Новая технология может работать в сочетании с другими перспективными разработками, такими как стеклянные подложки и кремниевая фотоника. Первые устройства с CoPoS могут появиться на рынке к концу 2029 года.

Источник: ComputerBase

0 комментариев