Samsung Electronics преодолела барьер 10 нм в производстве DRAM: впервые получены рабочие пластины

Samsung Electronics совершила прорыв в технологии производства DRAM, впервые успешно получив рабочие пластины на уровне менее 10 нанометров.

Это достижение знаменует собой ключевой шаг в преодолении «10-нанометрового проклятия» DRAM.

По данным отраслевых источников, в прошлом месяце Samsung Electronics изготовил пластины по технологии 10a, а в ходе тестирования характеристик чипов подтвердил наличие рабочих пластин. Это результат первого применения компанией структуры ячейки 4F² и технологии вертикального канального транзистора (VCT).

В индустрии DRAM поколения на 10 нм принято делить на 1x, 1y, 1z, 1a, 1b, 1c, 1d.

10a — это следующий узел после 1d, первый суб-10-нанометровый узел. По оценкам экспертов, реальная ширина линий составляет около 9,5–9,7 нм.

Рабочая пластина означает, что часть чипов, вырезанных из пластины, функционирует в соответствии с проектом. Получение рабочих пластин на этапе разработки считается сигналом правильности конструкции и технологического направления. После этого будут проводиться работы по повышению выхода и верификации надёжности.

Samsung Electronics планирует завершить разработку DRAM 10a на основе этой структуры в текущем году, провести испытания качества в следующем году, а в 2028 году — перенести технологию на производственные линии.

Компания намерена использовать структуры 4F² и VCT в трёх поколениях: 10a, 10b и 10c, а с поколения 10d перейти на 3D DRAM.

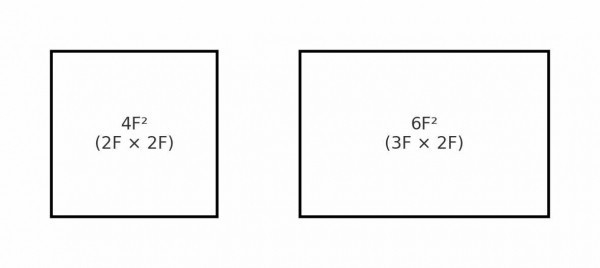

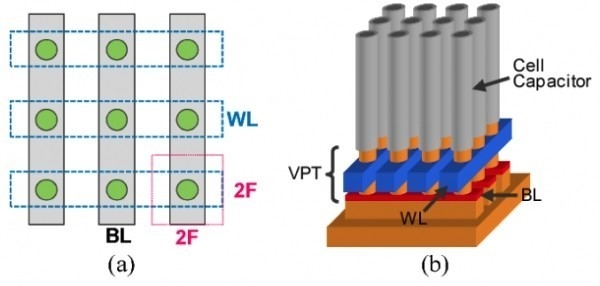

Ключ к прорыву — две новые технологии: площадь ячейки 4F² и вертикальный канальный транзистор. Ранее площадь ячейки DRAM составляла 6F², а в 10a она уменьшена до 4F². Теория показывает, что при одинаковом размере кристалла переход на 4F² позволяет разместить на 30–50% больше ячеек, что увеличивает ёмкость, скорость и снижает энергопотребление. Чтобы разместить затвор, канал и конденсатор на уменьшенной площади, Samsung внедрила технологию VCT, при которой конденсатор располагается над транзистором — это меняет традиционную компоновку, где они занимали отдельные участки.

С применением 4F² и VCT изменился и основной материал. Samsung заменил кремний канала на IGZO (оксид индия-галлия-цинка), чтобы подавить токи утечки в уменьшенной ячейке и обеспечить характеристики удержания данных. Кроме того, различные периферийные схемы, расположенные вокруг ячейки, будут обрабатываться отдельно на пластинах и соединяться по технологии гибридного бондинга пластина-к-пластине (PUC-схема).

Отраслевые эксперты отмечают, что успешное получение рабочих пластин означает ускорение разработки и внедрения этой технологии у Samsung Electronics. В то же время стратегии других производителей различаются. Micron планирует максимально долго сохранять существующую конструкцию. Китайские производители DRAM, не имеющие возможности импортировать оборудование EUV-литографии, в текущих условиях испытывают трудности с уменьшением ширины линий, поэтому активно разрабатывают 3D DRAM, рассчитывая, что после перехода на 3D-архитектуру можно будет производить передовые продукты с использованием традиционных литографических машин. SK hynix, в свою очередь, планирует применить 4F² и VCT не в узле 10a, а в 10b.

0 комментариев