Alchip и Ayar Labs представили первое оптическое решение на базе TSMC COUPE для ИИ-чипов

На европейском форуме TSMC Open Innovation Platform (OIP) на этой неделе компании Alchip и Ayar Labs продемонстрировали первое в отрасли полностью интегрированное оптическое решение для чипов следующего поколения. Оно построено на платформе TSMC COUPE и предназначено для обеспечения оптической связи в ИИ-ускорителях.

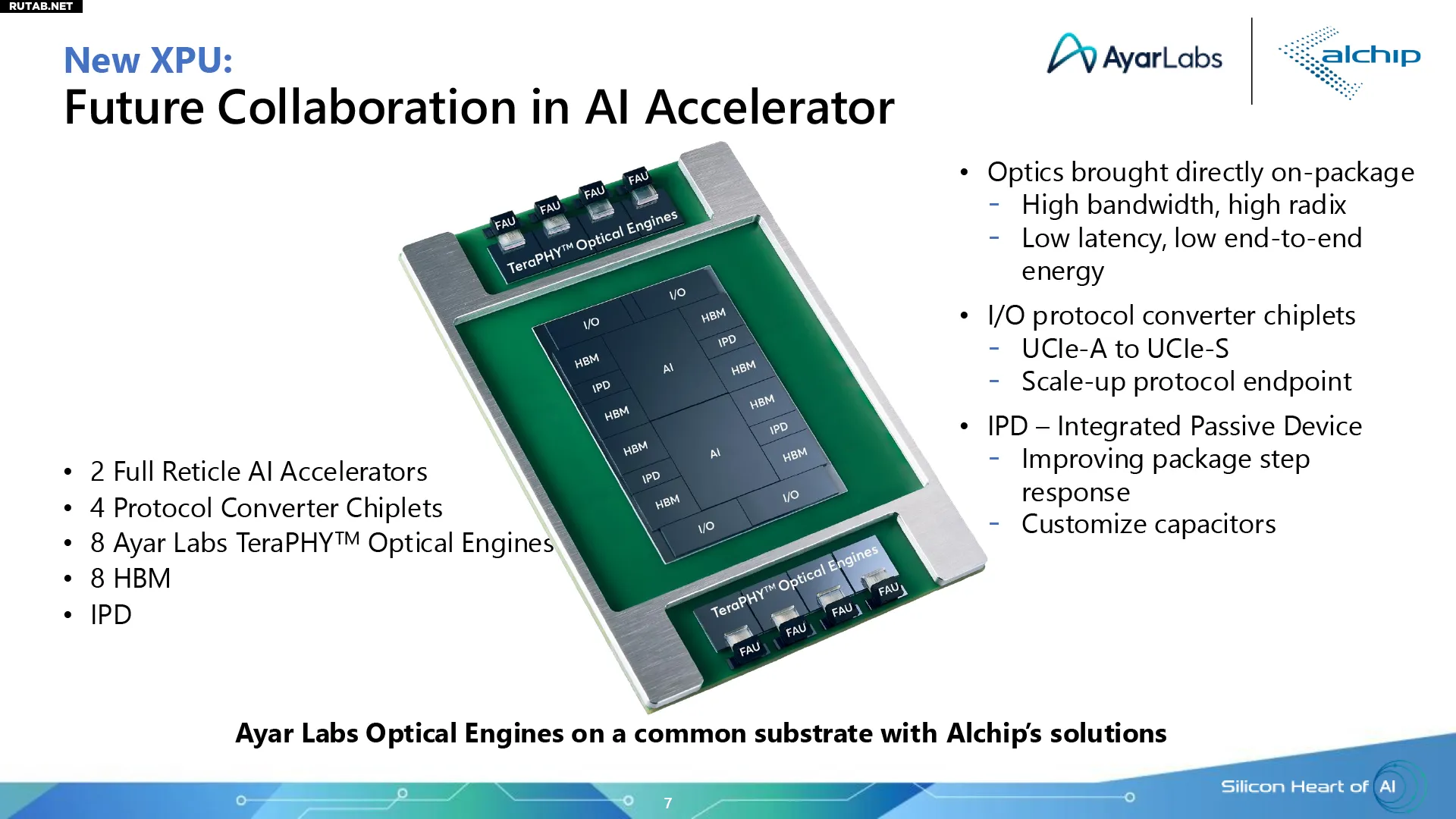

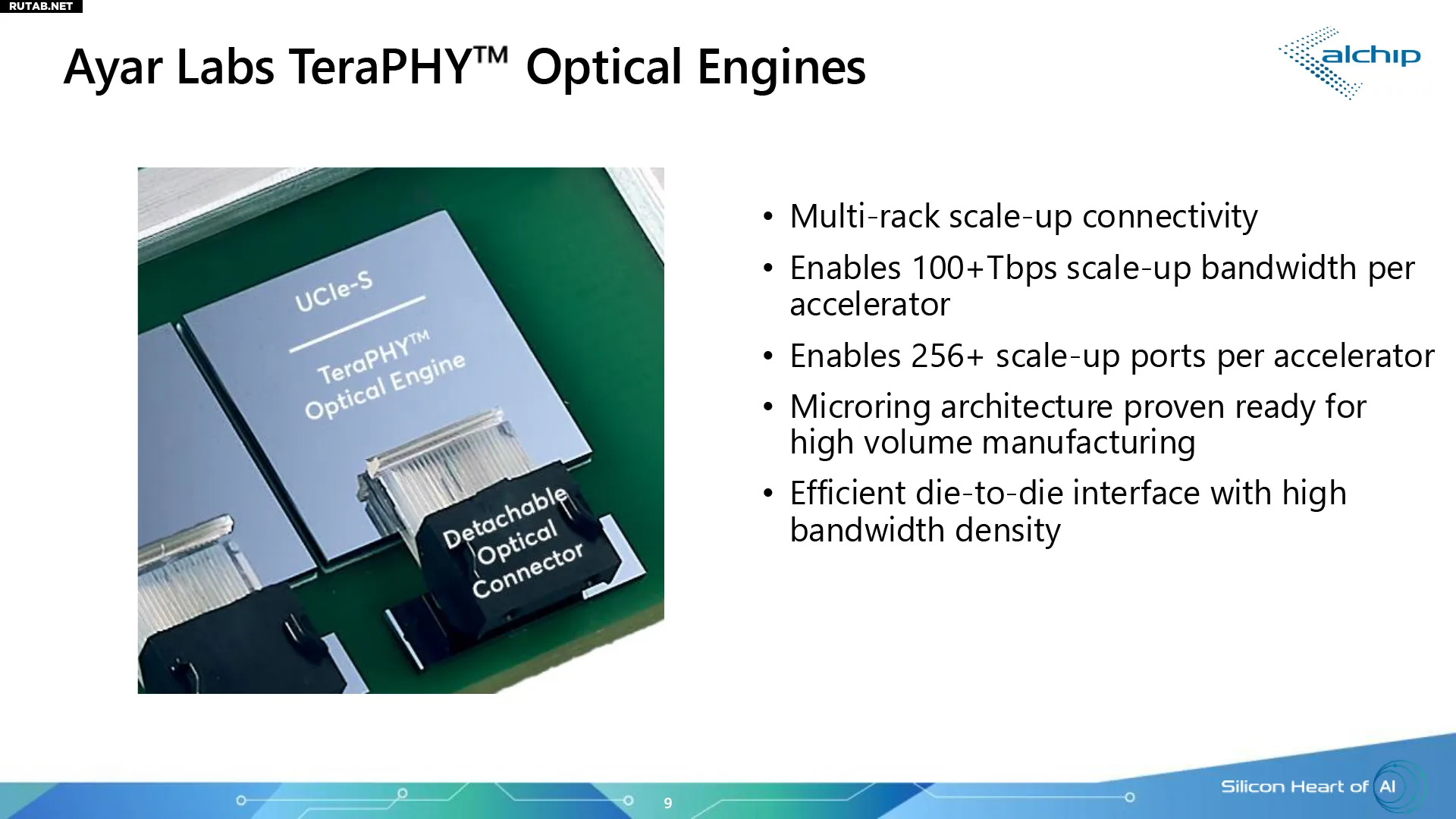

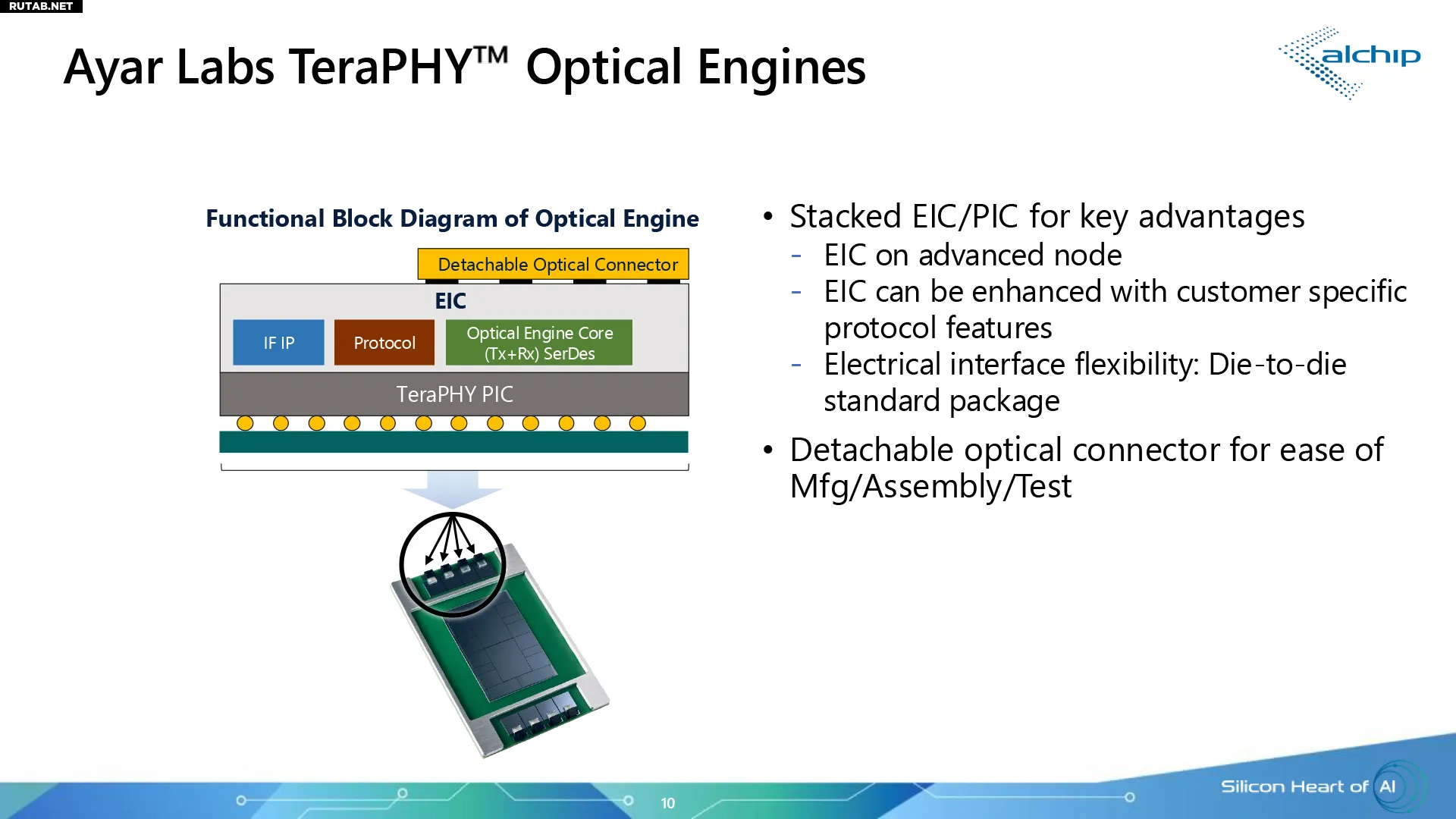

Решение представляет собой упакованный оптический подсистему ввода-вывода, которая сочетает в себе фотонный чип TeraPHY от Ayar Labs на базе кремниевой фотоники, электрический интерфейсный кристалл от Alchip и съёмный волоконно-оптический разъём. По заявлению разработчиков, система способна обеспечить пропускную способность до 100 Тбит/с на один ускоритель и подключаться к другим чипам с помощью отраслевого стандарта UCIe.

Платформа TSMC COUPE, представленная в 2024 году, изначально была нацелена на крупных разработчиков, таких как AMD или Nvidia, которые могут позволить себе создавать собственные электронные и фотонные интегральные схемы. Однако многие создатели специализированных ускорителей не имеют ресурсов для такой вертикальной интеграции. Готовое решение от Alchip и Ayar Labs позволяет небольшим компаниям относительно легко добавить оптическую связь в свои чипы, не вкладывая десятки миллионов долларов в разработку с нуля.

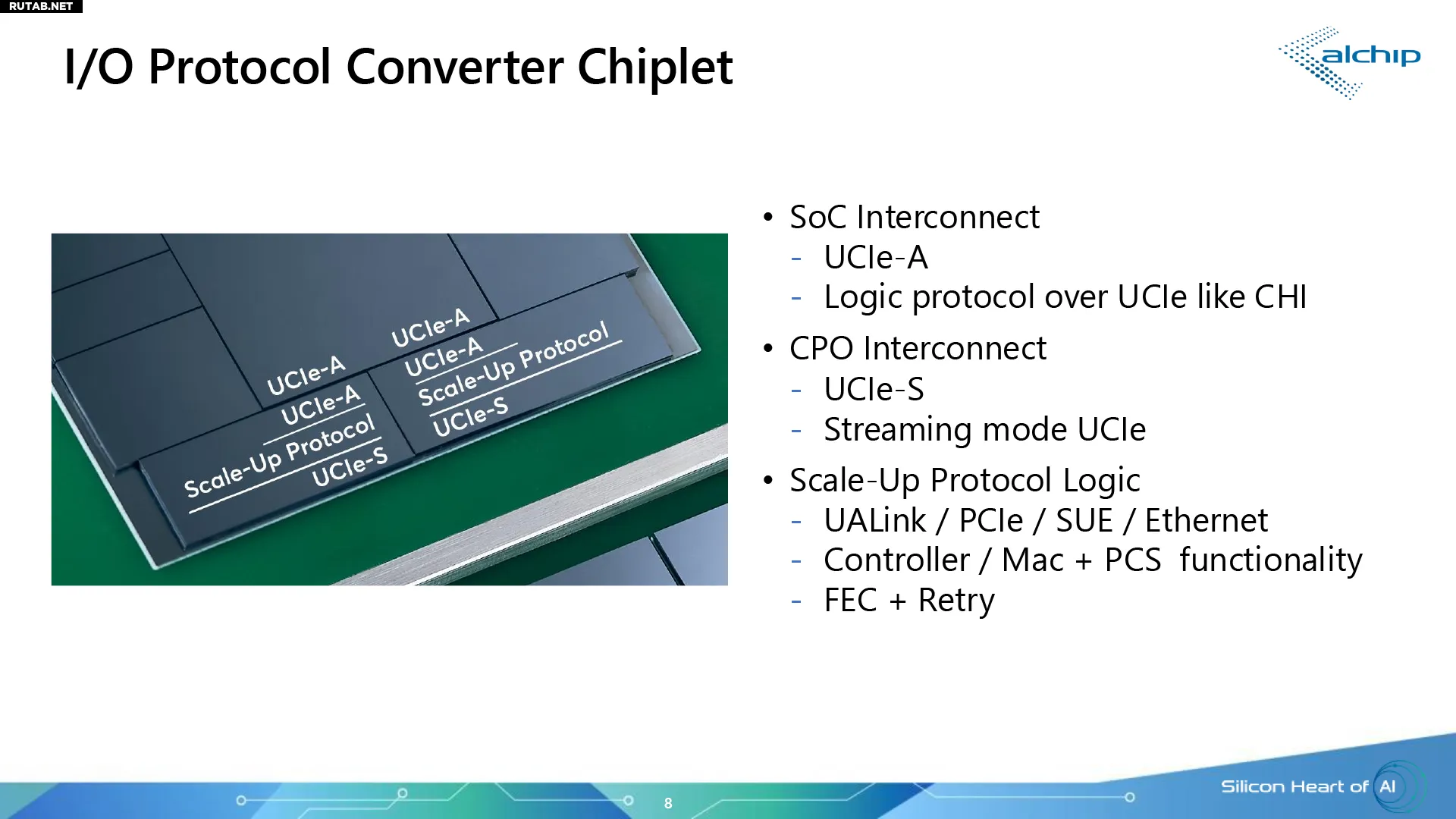

Совместно разработанная подсистема состоит из трёх чиплетов: конвертера протоколов от Alchip, электрического интерфейсного кристалла (EIC) и фотонного чипа (PIC) TeraPHY. Конвертер протоколов работает с интерфейсом UCIe-A акселератора и поддерживает масштабируемые протоколы, такие как UALink, PCIe и Ethernet. Фотонный чип использует архитектуру микроколец и поставляется со съёмными оптическими разъёмами.

Оптическая подсистема поддерживает экстремальное масштабирование: более 100 Тбит/с пропускной способности на ускоритель и более 256 оптических портов на устройство. Это позволяет соединять сотни процессоров в нескольких стойках, работающих как один большой процессор. Также решение потенциально может использоваться для расширителей памяти.

Согласно схеме Alchip, платформа может обеспечивать соединения типа «XPU-to-XPU», «XPU-to-коммутатор» и «коммутатор-to-коммутатор». Продаваясь в виде чиплетов, это решение открывает для небольших разработчиков ИИ-ускорителей доступ к сверхвысокой пропускной способности, низкой задержке и энергоэффективным соединениям в масштабах целой стойки или даже нескольких стоек.

Источник: Tomshardware.com

0 комментариев