NVIDIA переосмысливает ИИ: скорость до 20 000 токенов в секунду на пользователя, энергопотребление снижено в 1000 раз

Если в предыдущие годы акцент в области ИИ делался на обучении моделей, то сейчас ключевым направлением стал инференс (вывод). На прошедшей на прошлой неделе конференции GTC компания NVIDIA представила новый чип LPU, призванный переосмыслить подход к ИИ-инференсу.

Во время мероприятия состоялась глубокая дискуссия между главным учёным NVIDIA Биллом Далли и главным учёным Google Джеффом Дином. Далли поделился некоторыми деталями исследований NVIDIA в этой области.

Инференс ИИ предъявляет высокие требования к задержкам. Далли отметил, что сейчас узким местом является уже не вычислительная мощность сама по себе, а коммуникационные накладные расходы. NVIDIA исследует статическое планирование внутричиповой коммуникации, что позволит полностью устранить затраты на маршрутизацию, очереди и арбитраж, приблизив скорость передачи данных к скорости света.

В современных решениях задержка при передаче сигнала из одного угла чипа в другой может составлять сотни наносекунд. Технология NVIDIA позволяет сократить её до 30 наносекунд.

Что касается межчиповой связи, предыдущий подход заключался в постепенном увеличении пропускной способности — сейчас достигнуты показатели в 400 Гбит/с и даже 800 Гбит/с. Однако такая высокая пропускная способность требует сложной обработки сигналов и механизмов коррекции ошибок. Если же снизить скорость, например, с 400 Гбит/с до 200 Гбит/с, эти сложные проблемы исчезают, и задержка, связанная только с последовательной передачей, может быть выполнена за несколько тактов.

Далли выразил уверенность, что в будущем скорость инференса ИИ может достичь 10 000–20 000 токенов в секунду для одного пользователя. Для сравнения, текущая скорость вывода у большинства крупных языковых моделей для пользователей обычно не превышает 100 токенов в секунду, и даже скорость выше 60 токенов в секунду уже считается высокой.

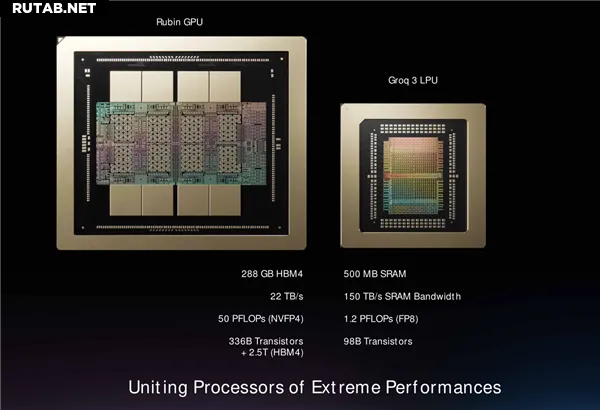

Далли подчеркнул, что достижение такой скорости возможно только при использовании правильной архитектуры. В качестве примера он привёл точность NVFP4: выполнение одной операции умножения-сложения с такой точностью потребляет около 10 фемтоджоулей энергии, в то время как чтение данных из внешней памяти HBM4 требует примерно 15 пикоджоулей — разница более чем в 1000 раз.

При использовании кэша на основе SRAM энергопотребление при чтении данных также снижается до уровня около 10 фемтоджоулей, что сравнимо с затратами на вычисления.

Однако у SRAM есть и свои недостатки: стоимость чипов с такой памятью будет выше, чем с HBM. Представленный на GTC чип LPU30 (LPU) от NVIDIA может интегрировать только 500 МБ кэша SRAM, что несопоставимо с 288 ГБ памяти HBM4, интегрируемой в GPU.

0 комментариев