TSMC подтверждает отсутствие необходимости в High-NA EUV для 1,4-нм техпроцесса

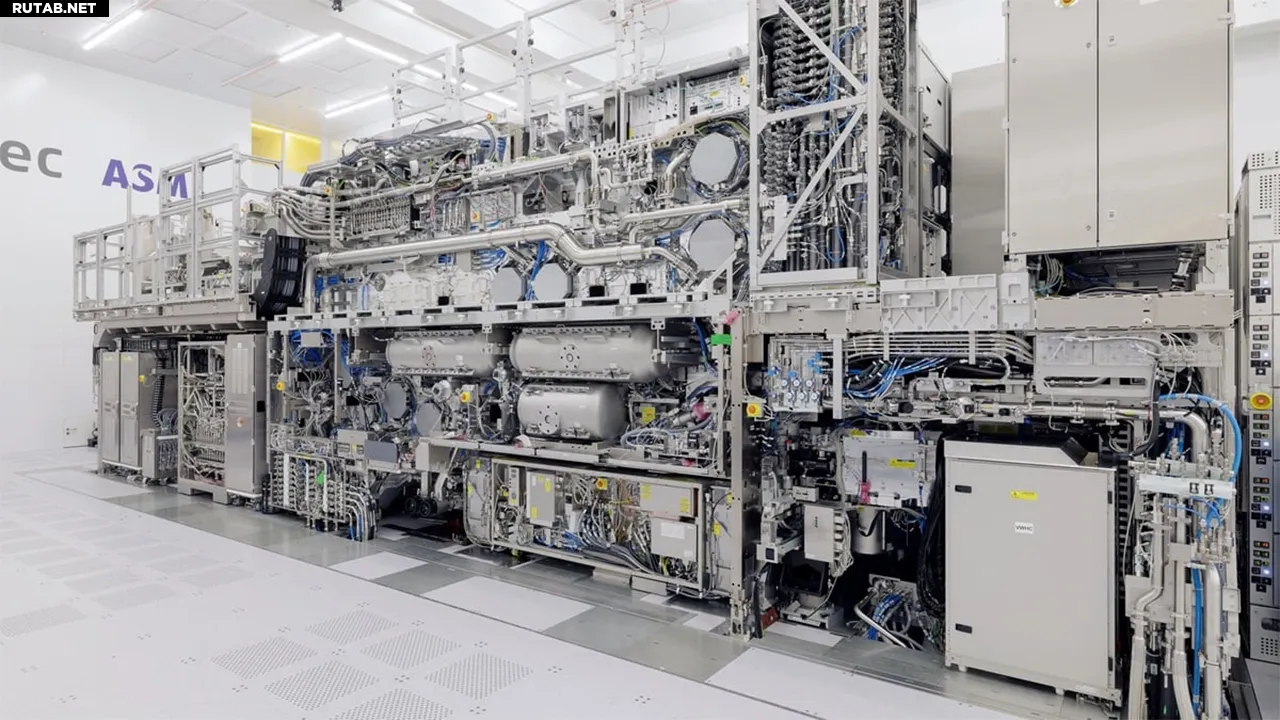

TSMC вновь подтвердила свою позицию по поводу использования оборудования High-NA EUV для производства чипов по новейшим техпроцессам. Компания заявила, что не планирует применять эти литографические системы для узлов A16 (1,6 нм) и A14 (1,4 нм).

«Людей всегда интересует, когда TSMC начнёт использовать High-NA, но наш ответ прост», — заявил Кевин Чжан, заместитель COO и старший вице-президент по развитию бизнеса и глобальным продажам. «Мы внедрим эту технологию, только когда увидим в ней значимые преимущества. В случае с A14 нам удалось добиться существенного прогресса без High-NA. Наша команда продолжает искать способы продлить срок службы текущего EUV-оборудования».

Техпроцесс A14 основан на транзисторах второго поколения с архитектурой nanosheet gate-all-around и новой структурой стандартных ячеек. По данным TSMC, он обеспечивает:

- +15% производительности при том же энергопотреблении;

- снижение энергопотребления на 25–30% при той же частоте;

- увеличение плотности транзисторов на 20–23% по сравнению с N2.

Несмотря на такие показатели, TSMC не потребуется High-NA EUV для массового производства чипов по техпроцессам A16 и A14. Примечательно, что A14 — это совершенно новый узел, который планируется к запуску в 2028 году.

«Это инновационное решение нашей команды, — отметил Чжан. — Пока мы находим способы обходиться без High-NA, мы не будем его использовать. Но в будущем, когда это станет экономически оправданным, мы внедрим эту технологию».

В отличие от Intel, которая начнёт применять High-NA EUV с техпроцессом 14A в 2027–2028 годах, TSMC не планирует переходить на эту технологию как минимум до 2030 года.

ИИ: Решение TSMC обойтись без дорогостоящего оборудования High-NA EUV демонстрирует её технологическую гибкость. Это может дать компании преимущество в стоимости производства, хотя Intel, вероятно, получит выгоду от более продвинутой литографии в долгосрочной перспективе.

0 комментариев