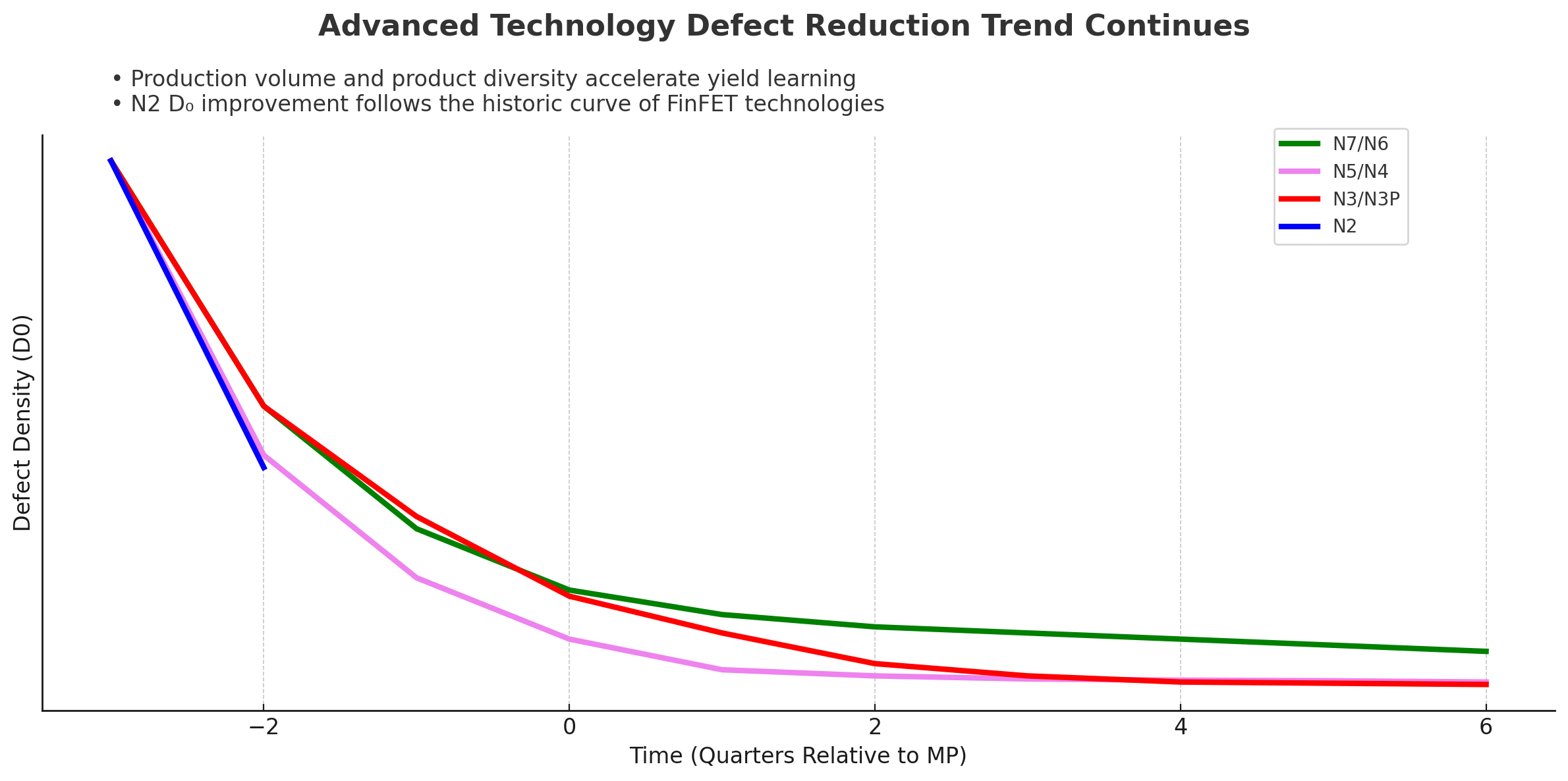

TSMC раскрывает плотность дефектов N2 — ниже, чем N3 на той же стадии разработки

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

Читайте также:SK hynix представила HBM4 на симпозиуме TSMC 2025TSMC планирует выпуск сверхмощных процессоровTSMC начнёт выпуск 2-нм процессоров в этом годуM31 сотрудничает с TSMC для продвижения 2-нм IP-инноваций eUSB2Cadence и TSMC совершенствуют проектирование микросхем

Хотя N2 от TSMC является первой технологической технологией компании, которая приняла нанолистовые транзисторы gate-all-around (GAA), узел имеет более низкую плотность дефектов, чем его предшественники на той же стадии разработки, за два квартала до массового производства (MP). Предшественники — N3/N3P, N5/N4 и N7/N6 — все полагались на известные транзисторы FinFET. Таким образом, несмотря на то, что это первый узел TSMC, использующий нанолистовые транзисторы GAA, плотность дефектов N2 снижается быстрее (ну, круче), чем у его предшественников до рубежа массового производства (HVM).

Изображение: Данные TSMC, перерисованы DALL-E/Chat-GPT.

На диаграмме показана плотность дефектов в зависимости от времени, охватывающая период от трех кварталов до массового производства до шести кварталов после MP. Во всех показанных узлах — N7/N6 (зеленый), N5/N4 (фиолетовый), N3/N3P (красный) и N2 (синий) — плотность дефектов значительно снижается по мере роста производства, хотя и с разной скоростью в зависимости от сложности узла. Примечательно, что N5/N4 продемонстрировал наиболее агрессивное раннее снижение дефектов, в то время как N7/N6 продемонстрировал более постепенное улучшение выхода годных. Кривая N2 начинается с более высоких начальных уровней дефектов, чем N5/N4, но резко снижается, близко соответствуя траектории снижения дефектов N3/N3P.

На слайде подчеркивается, что объем производства и разнообразие продукции остаются ключевыми факторами для ускорения улучшения плотности дефектов. Большие объемы производства и широкий ассортимент продукции, использующей один и тот же процесс, позволяют быстрее выявлять и устранять проблемы плотности дефектов и выхода годных, что позволяет TSMC оптимизировать циклы обучения дефектам. TSMC заявила, что ее технология изготовления N2 получила больше новых выходов ленты, чем предшественники (поскольку TSMC теперь рискует производить чипы N2 для смартфонов и клиентов HPC), поэтому кривая снижения плотности дефектов в основном это доказывает.

Тот факт, что скорость снижения дефектов N2 хорошо согласуется с предыдущими узлами на основе FinFET, особенно важен, учитывая факторы риска, связанные с внедрением совершенно новой архитектуры транзисторов. Это говорит о том, что TSMC успешно перенесла свой опыт обучения процессам и управления дефектами в новую эру GAAFET без серьезных неудач (по крайней мере, на основе того, что раскрывает TSMC).

Источник: Tomshardware.com

0 комментариев