Интерпозер CoWoS TSMC Super Carrier увеличивается

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

Читайте также:Обновление TSMC 1.6 нм: ощутимые улучшения, но возникают новые проблемыTSMC: разработка 2-нм чипов с улучшенной производительностью1,6-нм узел TSMC будет готов к производству в конце 2026 годаСанкции США заморозили производство чипов Huawei Ascend AITSMC обнаружила неразорвавшуюся бомбу на строительной площадке завода по производству микросхем в Гаосюне

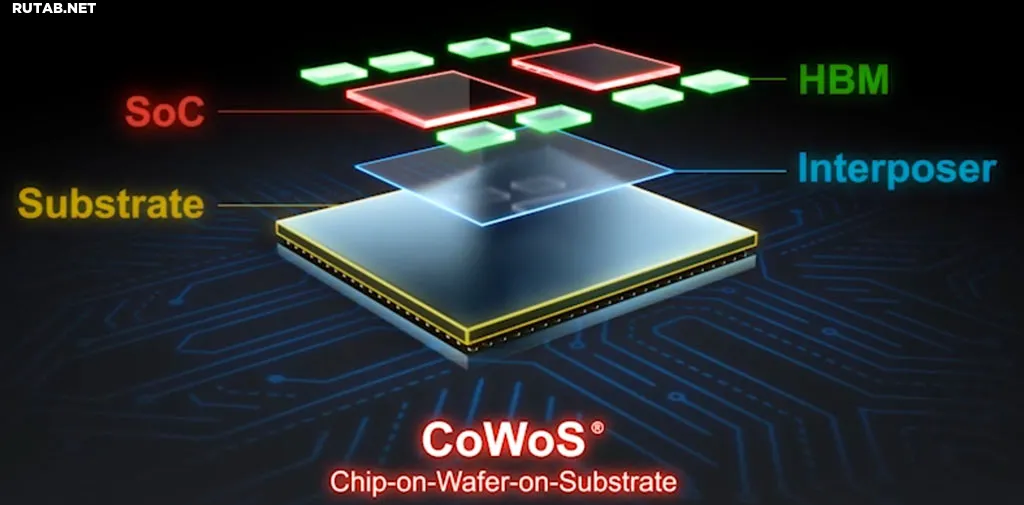

TSMC ежегодно внедряет новые технологические процессы, делая все возможное для удовлетворения потребностей своих клиентов в улучшении мощности, производительности и площади (PPA). Но некоторым клиентам требуется еще большая производительность, и для них предел сетки инструмента EUV-литографии в 858 мм^2 недостаточен. Эти клиенты предпочитают использовать многочиповые решения, упакованные с использованием технологии CoWoS TSMC, и в последние годы компания предложила несколько итераций этого метода.

Изображение: TSMC

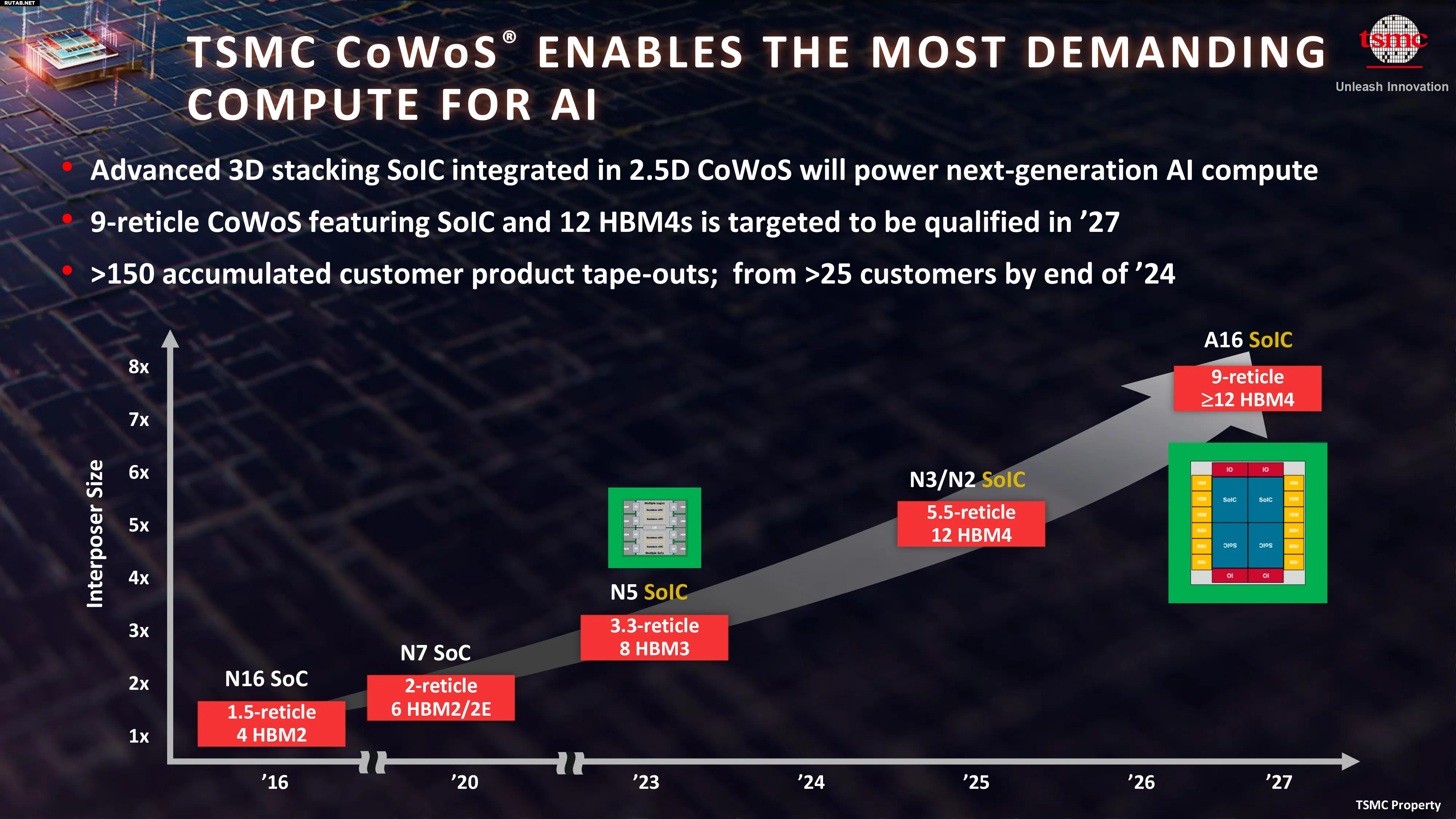

Первоначальный CoWoS позволял использовать чипы размером около 1,5 сетки в 2016 году, затем он эволюционировал до размера сетки 3,3 сегодня, что позволяет размещать восемь стеков HBM3 в пакете. Далее, TSMC обещает пакеты размером сетки 5,5 с 12 стеками памяти HBM4 в 2025–2026 годах. Однако это меркнет по сравнению с окончательной версией CoWoS компании, которая позволяет использовать системы-в-пакетах (SiP) размером до девяти сеток с 12 и потенциально большим количеством модулей HBM4 на борту.

Планируется, что 9-точечный «Super Carrier» CoWoS (предлагающий до 7722 мм^2 для чиплетов и памяти) с 12 стеками HBM4 будет сертифицирован в 2027 году, поэтому разумно ожидать, что он будет принят в 2027–2028 годах для сверхмощных процессоров ИИ.

TSMC полностью ожидает, что компании, внедряющие ее передовые методы упаковки, также будут вертикально размещать свою логику, используя ее передовые технологии упаковки системных интегральных схем (SoIC) для дальнейшего увеличения количества транзисторов и производительности. Фактически, с 9-сетчатым CoWoS, TSMC ожидает, что ее клиенты будут размещать кристалл класса 1,6 нм поверх кристалла класса 2 нм, поэтому мы говорим об очень высокой плотности транзисторов.

Однако с этими сверхбольшими пакетами CoWoS есть одна серьезная проблема. Пакет CoWoS с 5,5 сетками потребует подложку размером более 100x100 мм (что приближается к ограничениям по размеру стандарта OAM 2.0, который измеряет 102x165 мм), тогда как CoWoS с 9 сетками выйдет за рамки подложки размером 120x120 мм. Такие крупные размеры подложки повлияют на то, как проектируются системы и как центры обработки данных будут оснащены для их поддержки. В частности, на питание и охлаждение. Когда речь идет о питании, мы говорим о сотнях киловатт на стойку, тогда как когда речь идет об охлаждении, мы говорим о жидкостном охлаждении и методах погружения для эффективного управления мощными процессорами.

Источник: Tomshardware.com

0 комментариев