Обновление TSMC 1.6 нм: ощутимые улучшения, но возникают новые проблемы

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

Читайте также:TSMC: разработка 2-нм чипов с улучшенной производительностью1,6-нм узел TSMC будет готов к производству в конце 2026 годаСанкции США заморозили производство чипов Huawei Ascend AITSMC обнаружила неразорвавшуюся бомбу на строительной площадке завода по производству микросхем в ГаосюнеIntel увеличивает заказы на «Arrow Lake» в TSMC

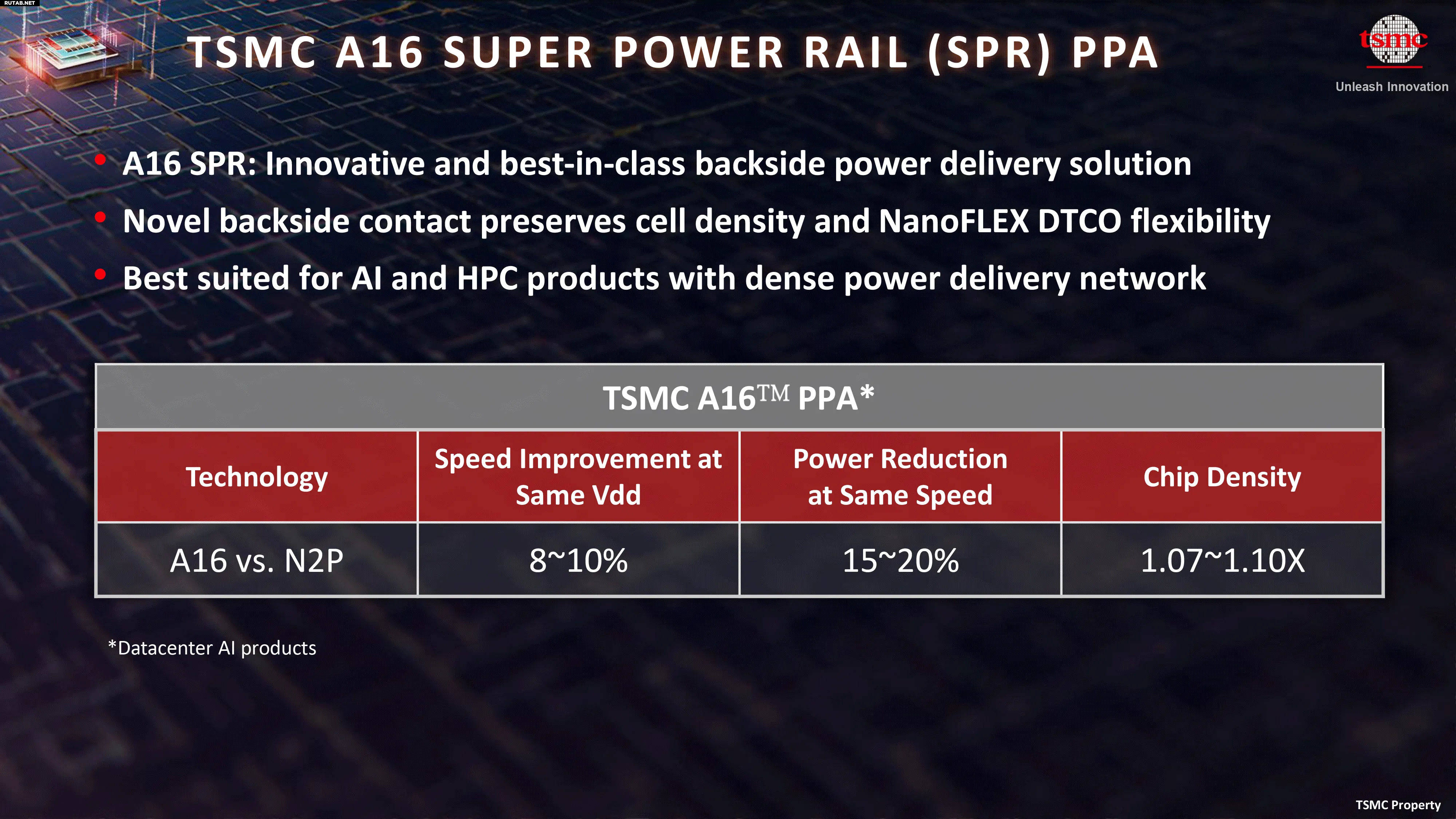

Процесс A16 от TSMC будет использовать нанолистовые транзисторы gate-all-around (GAAFET) с архитектурой, аналогичной тем, которые представлены в технологиях TSMC серии N2 (класс 2 нм), и включать заднюю шину питания для улучшения подачи питания и повышения плотности транзисторов. По сравнению с технологией изготовления N2P, A16 обещает прирост производительности на 8%-10% при том же напряжении и сложности или снижение энергопотребления на 15%-20% при той же частоте и количестве транзисторов. Кроме того, TSMC оценивает увеличение плотности чипов в 1,07x-1,10x для высокопроизводительных процессоров ИИ в зависимости от типов транзисторов и используемых библиотек.

Изображение: TSMC

По словам Кена Вана, директора TSMC по исследованию конструкторских решений и технологическому бенчмаркингу, с точки зрения архитектуры транзисторы A16 аналогичны транзисторам N2. Это упрощает переход на этот технологический процесс с N2.

«Переход логической компоновки с N2P на A16 на самом деле довольно прост, поскольку структура ячеек и большинство шаблонов компоновки совершенно одинаковы», — сказал Ван. «Так что, помимо сохранения той же структуры лицевой стороны, прелесть A16 в том, что он наследует функцию NanoFlex от модуляции ширины устройства N2 для максимальной мощности привода».

Super Power Rail от TSMC подключает заднюю сеть питания напрямую к источнику и стоку каждого транзистора через специализированный контакт, минимизируя длину и сопротивление проводов для максимизации производительности и энергоэффективности. С точки зрения производства эта реализация является одной из самых сложных конструкций BSPDN, превосходя по сложности Intel Power Via.

Изображение: TSMC

Однако расширенная реализация BSPDN также означает, что проектировщики чипов должны полностью перепроектировать свою сеть подачи питания, проложить ее по-новому и, следовательно, применить новые стратегии размещения и маршрутизации, что и следовало ожидать. Кроме того, им придется предпринять некоторые меры по снижению температуры, поскольку горячие точки чипа теперь будут располагаться под набором проводов, что затрудняет рассеивание тепла.

Проектирование чипов с задней PDN по сути означает принятие новых методов реализации, поскольку многое меняется, включая сам поток проектирования. Ван упомянул использование нового программного обеспечения с учетом температуры, размещения и маршрутизации, новую конструкцию дерева тактовых импульсов, другой анализ IR-Drop, разнородные домены питания и другой вывод термического анализа, среди прочего.

Учитывая новый поток внедрения, требуются новые версии инструментов EDA и программного обеспечения для моделирования. Поскольку мы говорим об узле, похожем на N2 от TSMC, многие вещи уже готовы, хотя и в версии инструментов EDA до 0.5 от ведущих производителей, таких как Cadence и Synopsys.

«A16 — это технология, подходящая для проектов со сложными маршрутами и плотной PDN», — сказал Ван. «Однако она также создает новые проблемы, поэтому необходимы дополнительные усилия по проектированию. Наш VB с обратной стороны контакта также нуждается в полной проверке кремния с усердием. В то же время у нас есть комплексная программа поддержки A16 EDA, которая продолжается, и мы продолжим обновлять статус A16 EDA».

Источник: Tomshardware.com

0 комментариев