AMD улучшит производительность видеокарт RDNA 5 за счёт оптимизации двойного исполнения инструкций

Следующее поколение видеокарт Radeon от AMD, архитектура RDNA 5, ожидается как значительный шаг вперёд по сравнению с RDNA 4. Одна из проблем, которую, судя по всему, решает «красная команда», — это эффективность двойного исполнения инструкций (dual-issue execution). Эта функция, позволяющая графическому процессору выполнять две инструкции за один такт, присутствует в картах AMD начиная с RDNA 3, но жёсткие правила спаривания инструкций не всегда позволяли компиляторам ею воспользоваться, ограничивая теоретическую пиковую производительность. Новый патч для компилятора LLVM указывает на то, что AMD решит эту проблему в RDNA 5.

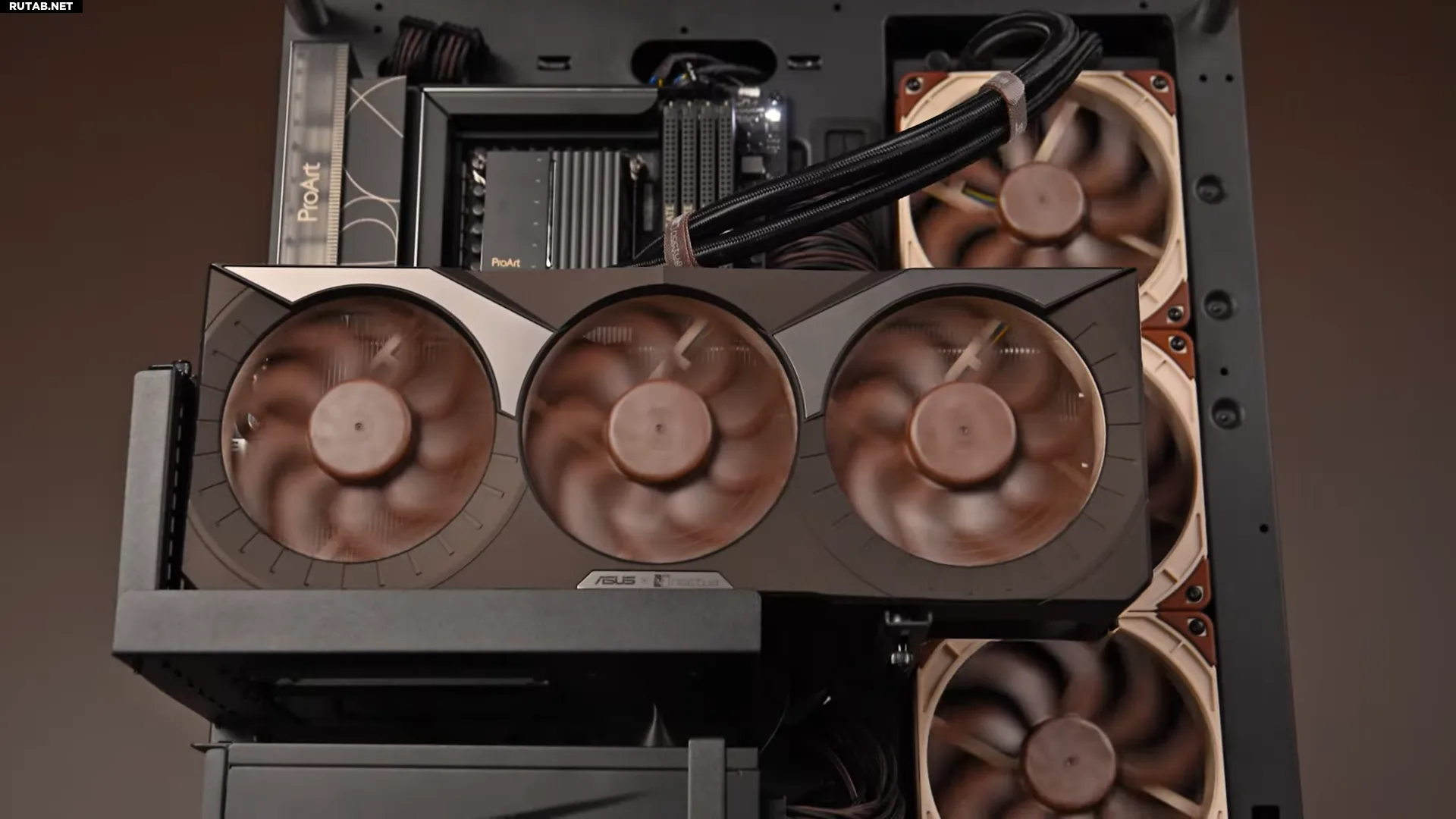

Изображение: Noctua

Ресурс Coelacanth's Dream, специализирующийся на Linux, изучил изменения и обнаружил, что они ссылаются на gfx13, который является производным от gfx130, то есть RDNA 5. Похоже, AMD добавляет новый формат инструкций под названием «VOPD3», предназначенный для более эффективного взаимодействия с двойным VALU (Векторным арифметико-логическим устройством; шейдерным блоком). Он должен быть более гибким, что упростит компилятору использование двойного исполнения инструкций.

На техническом уровне существующая система, известная как VOPD, в основном работала только с более простыми инструкциями на 2 операнда, что затрудняло для компиляторов планирование совместимых пар инструкций. VOPD3 расширит это до инструкций на 3 операнда, что позволит поддерживать такие операции, как совмещённое умножение-сложение (FMA). Фактически, инструкция V_FMA_F32 была добавлена именно в этом запросе на слияние, что и позволяет сделать вывод о её появлении в RDNA 5.

Это позволит двойному исполнению инструкций происходить чаще, что потенциально приведёт к значительному увеличению пропускной способности FP32 (в некоторых случаях). Шейдерные блоки будут меньше времени простаивать в ожидании тактов и вместо этого выполнять больше работы, повышая эффективность каждой инструкции. Это может помочь в требовательных сценариях, таких как рендеринг, а значит, игровые движки смогут оптимизироваться под двойной VALU.

Сокращение числа случаев, когда спаривание инструкций невозможно из-за ограничений, — ключевой шаг к повышению эффективности аппаратного обеспечения без грубого наращивания IPC за счёт увеличения площади кристалла. Инструкции FMA также важны для нейронного рендеринга, поэтому такие технологии, как апскейлинг и генерация кадров, также могут получить прирост, даже если само «железо» не станет производительнее — поскольку двойное исполнение инструкций повышает эффективность в любом случае.

Если вам интересны технические детали, вы можете ознакомиться со статьёй Coelacanth's Dream по ссылке выше, но будьте готовы к сложному материалу. Кроме того, выход RDNA 5 ожидается ещё не скоро, и более заметные для потребителей обновления, такие как большее количество вычислительных ядер, безусловно, будут более маркетинговыми чертами. Тем не менее, возможность графическому процессору легче и стабильнее достигать заявленной пропускной способности FP32 — это большая архитектурная победа.

Источник: Tomshardware.com

0 комментариев