Samsung представила экспериментальную архитектуру NAND с энергопотреблением ниже на 96%

Исследователи Samsung опубликовали детальное описание экспериментальной архитектуры NAND, которая может сократить один из основных источников энергопотребления этой технологии на целых 96%.

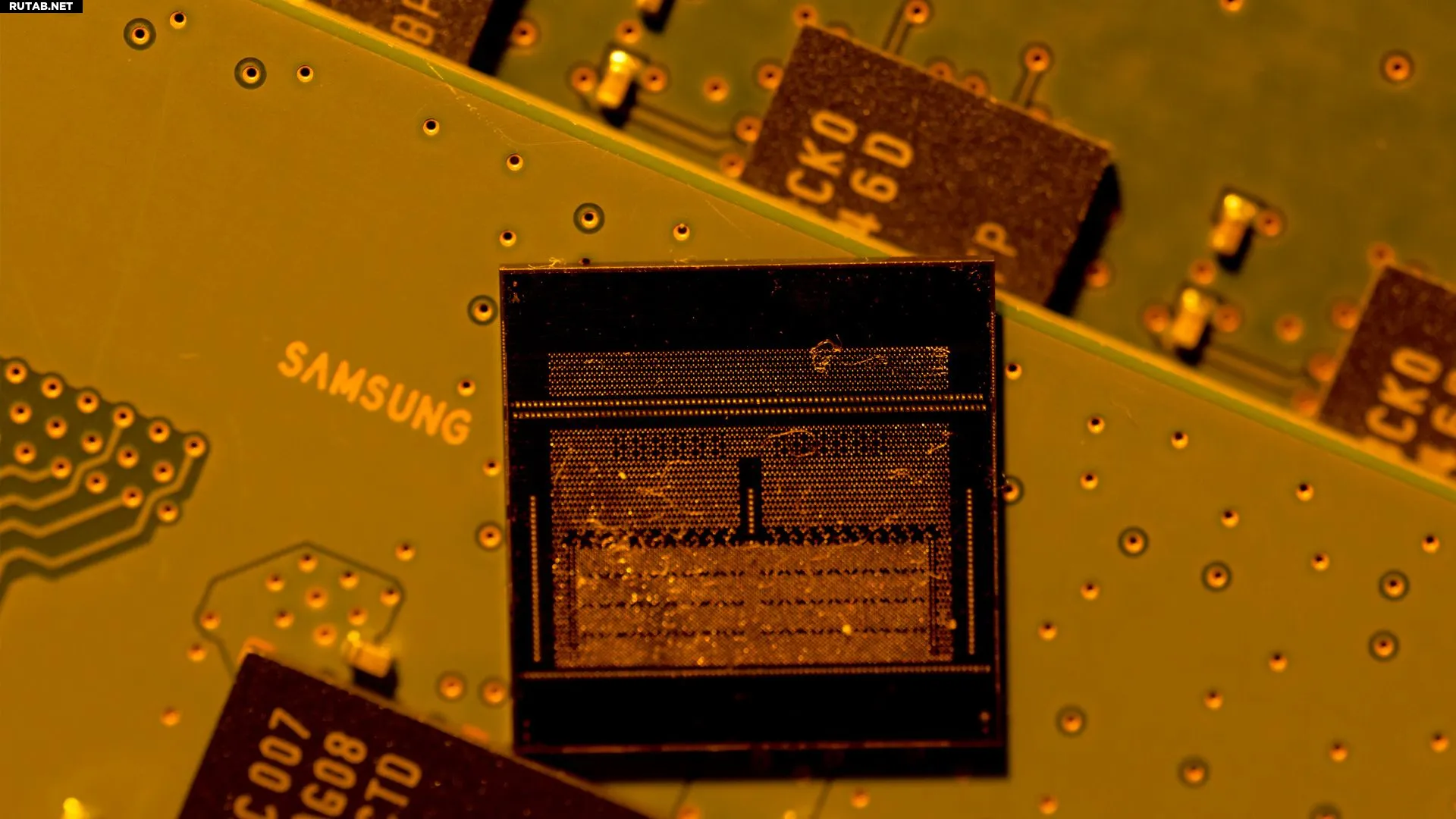

Работа под названием «Ферроэлектрический транзистор для энергоэффективной NAND-памяти» была выполнена специалистами из Samsung Advanced Institute of Technology и опубликована в журнале Nature. В ней описывается конструкция ферроэлектрического полевого транзистора (FeFET) для будущей 3D NAND, сочетающая ферроэлектрик на основе гафния с оксидным полупроводниковым каналом. Ключевым нововведением является режим работы с почти нулевым пассивным напряжением, который и лежит в основе заявленного 96-процентного снижения энергопотребления.

В современной NAND-памяти стопка линий слов, проходящих через каждую вертикальную цепочку ячеек, должна получать пассивное напряжение при каждом чтении или программировании ячейки. С ростом числа слоёв эти накладные расходы увеличиваются и теперь составляют значительную долю от общего энергопотребления массива. Команда Samsung утверждает, что ферроэлектрический транзистор с широким окном памяти и максимальным пороговым напряжением, смещённым ниже нуля, может поддерживать многоуровневую работу без высокого пассивного напряжения, на которое полагается традиционная NAND с захватом заряда для предотвращения помех.

Исследователи продемонстрировали это сначала на планарных массивах, работающих с плотностью до пяти бит на ячейку, а затем на короткой четырёхслойной вертикальной структуре, имитирующей геометрию 3D NAND. Центральные затворы в этой структуре имеют размер 25 нанометров, что сопоставимо с современными коммерческими устройствами. Группа определила специфичный для NAND показатель энергии, который объединяет основные факторы: ёмкость линий слов и внутренние зарядовые насосы, генерирующие высокие напряжения, необходимые для операций чтения и записи.

Смоделировав эти затраты для полного стека, исследователи оценили, что 286-слойное устройство на основе ферроэлектрической конструкции может сократить совокупное энергопотребление при программировании и чтении примерно на 94% по сравнению с традиционным стеком с захватом заряда той же высоты. При 1024 слоях снижение превышает 96%, поскольку более низкое пассивное напряжение резко уменьшает нагрузку на зарядовые насосы.

Эксперименты также охватывали вопросы сохранения данных и пределы циклов перезаписи. В планарном исполнении ферроэлектрические ячейки демонстрируют широкое окно памяти и пятиуровневое программирование, хотя выносливость при такой плотности пока умеренная. Конфигурация, эквивалентная PLC, выдерживает несколько сотен циклов, а использование, аналогичное QLC, приближается к тысяче циклов как при комнатной температуре, так и при 85 °C. Авторы отмечают, что для вывода полноценного 3D-массива в производство потребуется дальнейшая разработка схем подавления программирования и генерации отрицательного напряжения. Они также указывают, что поведение оксидного канала в условиях высокотемпературного стресса остаётся ключевой областью для последующей работы.

На данный момент нет никаких указаний на то, что Samsung планирует выпуск продуктов на основе этой разработки. Вместо этого исследование позиционируется как фундаментальная работа, которая сама требует дальнейшего развития, для потенциальных поколений энергоэффективной NAND-памяти, выходящих за рамки текущей дорожной карты технологий с захватом заряда.

Источник: Tomshardware.com

0 комментариев