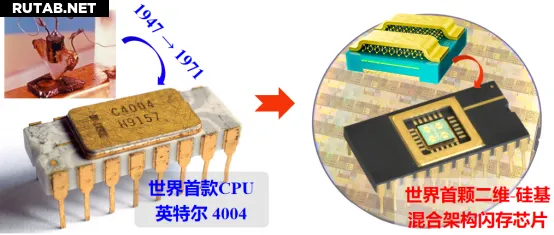

Разработан первый в мире 2D-кремниевый гибридный чип памяти

Команда Чжоу Пэна и Лю Чуньсэня из Инновационного института интегральных схем и микронаноэлектроники Национальной ключевой лаборатории интегральных чипов и систем при Фуданьском университете разработала новую архитектуру памяти под названием «Чанъин» (CY-01).

Эта разработка представляет собой глубокую интеграцию двумерных сверхбыстрых устройств памяти «Посяо» (PoX) со зрелой кремниевой CMOS-технологией, создав первый в мире двумерно-кремниевый гибридный чип.

Соответствующее исследование было опубликовано в журнале Nature 8 октября под названием «A full-featured 2D flash chip enabled by system integration» («Полнофункциональный чип флеш-памяти на основе двумерно-кремниевой гибридной архитектуры»).

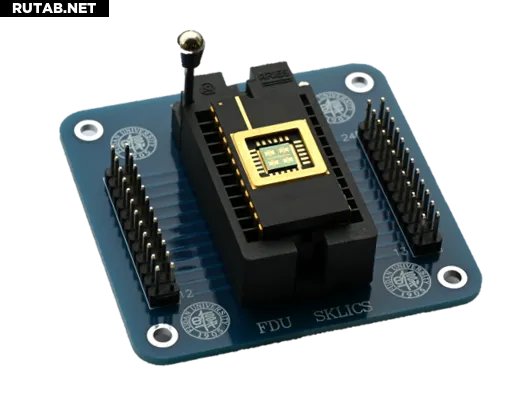

Упакованный двумерно-кремниевый гибридный чип памяти (с печатной платой)

В апреле этого года команда Чжоу Пэна и Лю Чуньсэня представила в журнале Nature прототип двумерного устройства памяти «Посяо», достигнув сверхвысокой скорости энергонезависимого хранения в 400 пикосекунд.

Это самая быстрая на сегодняшний день технология хранения полупроводникового заряда, но вопрос о том, как перейти от лаборатории к практическому применению, стал следующей сложной задачей.

Команда пришла к выводу, что для ускорения внедрения новых технологий необходимо полностью интегрировать двумерные сверхбыстрые устройства памяти в традиционные полупроводниковые производственные линии CMOS, поскольку CMOS-технология в настоящее время является основным процессом производства интегральных схем с очень зрелой цепочкой поставок.

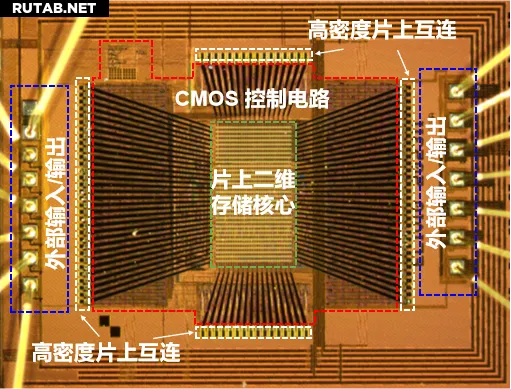

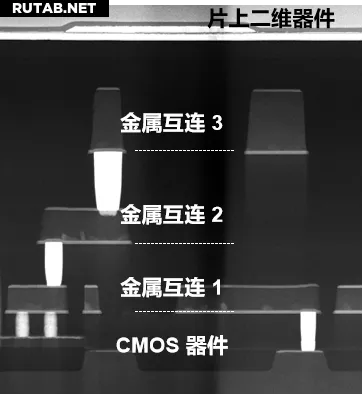

После пяти лет исследований команда решила проблему интеграции двумерных материалов с CMOS без ущерба для их производительности. Ключевым нововведением стал модульный подход: сначала двумерные схемы памяти и зрелые CMOS-схемы изготавливались отдельно, а затем соединялись с CMOS-схемами управления с помощью технологии высокоплотных межсоединений (микрометровые сквозные отверстия) для создания полного чипа.

Этот процесс обеспечил плотное прилегание двумерных материалов к CMOS-подложке на атомном уровне при сохранении высокого выхода годных изделий.

Команда также предложила методологию межплатформенного системного проектирования, включая совместное проектирование двумерных и CMOS-схем и проектирование межплатформенных интерфейсов, назвав эту систему интеграции «архитектурой Чанъин (CY-01)».

Полные испытания чипа на основе CMOS-схем, управляющих двумерным ядром памяти, подтвердили поддержку 8-битных операций, 32-битных высокоскоростных параллельных операций и случайной адресации с выходом годных изделий 94,3%.

Его производительность значительно превосходит текущую технологию флеш-памяти, впервые реализовав инженерную реализацию гибридной архитектуры.

На следующем этапе команда планирует создать экспериментальную базу, сотрудничать с соответствующими учреждениями для создания самостоятельных инженерных проектов и в течение 3-5 лет достичь уровня интеграции в мегамасштабе. Интеллектуальная собственность и IP, созданные в ходе этого процесса, могут быть лицензированы партнерским компаниям.

Оптическая микрофотография двумерно-кремниевого гибридного чипа памяти

Фотография двумерно-кремниевого гибридного чипа памяти, сделанная с помощью просвечивающего электронного микроскопа

0 комментариев