STMicroelectronics построит во Франции пилотную линию для передовой упаковки чипов

Компания STMicroelectronics, мировой лидер в производстве полупроводников, объявила о создании пилотной линии для разработки технологий панельного монтажа (Panel-Level Packaging, PLP) нового поколения. Новое производство разместится на площадке в Туре (Франция) и, как ожидается, заработает в третьем квартале 2026 года.

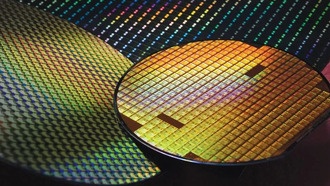

PLP — это передовая автоматизированная технология упаковки и тестирования чипов, которая повышает эффективность производства, снижает затраты и позволяет создавать более компактные, мощные и экономичные электронные устройства. В отличие от традиционных круглых кремниевых подложек, PLP использует большие прямоугольные панели, что значительно увеличивает пропускную способность производства. Развивая свою первую линию PLP в Малайзии и глобальную сеть НИОКР, ST планирует расширить применение этой технологии для автомобильной, промышленной и потребительской электроники.

«Развитие наших возможностей PLP в Туре направлено на продвижение этого инновационного подхода к упаковке и тестированию чипов, повышение эффективности и гибкости для широкого спектра применений, включая RF, аналоговые, силовые компоненты и микроконтроллеры. В программе задействована многопрофильная команда экспертов в области автоматизации производства, разработки процессов, анализа данных, а также технологических и продуктовых НИОКР. Это ключевая часть более масштабной стратегической инициативы, ориентированной на гетерогенную интеграцию — масштабируемый и эффективный новый подход к интеграции чипов», — заявил Фабио Гуаландрис, президент по качеству, производству и технологиям STMicroelectronics.

Создание новой пилотной линии PLP в Туре поддержано капиталовложениями в размере более 60 млн долларов США (~4,8 млн рублей), уже выделенными в рамках общекорпоративной программы по реструктуризации производственных мощностей компании. Ожидается синергия с местной экосистемой НИОКР, включая исследовательский центр CERTEM.

Техническая справка: Панельный монтаж (PLP) — это метод, при котором несколько интегральных схем упаковываются на одной большой прямоугольной подложке-панели, а не на отдельных круглых пластинах. Это позволяет обрабатывать больше чипов одновременно, снижая затраты и повышая производительность. Технология ST фокусируется на прямом медном соединении (Direct Copper Interconnect, DCI), которое заменяет традиционные проволочные соединения. Медь обеспечивает превосходную электропроводность, уменьшает потери мощности, улучшает теплоотвод и позволяет миниатюризировать устройства.

0 комментариев