Дорожная карта памяти HBM4-HBM8: до 64 ТБ/с и 240 ГБ на стек к 2038 году

На совместном брифинге на этой неделе лаборатория Memory Systems Laboratory KAIST и группа TERA Interconnection and Packaging представили перспективную дорожную карту развития стандартов памяти High Bandwidth Memory (HBM) и ускорителей, которые будут их использовать. Как сообщают Wccftech и VideoCardz, план охватывает пять поколений — от HBM4 до HBM8, каждое из которых обещает значительный рост емкости, пропускной способности и сложности упаковки.

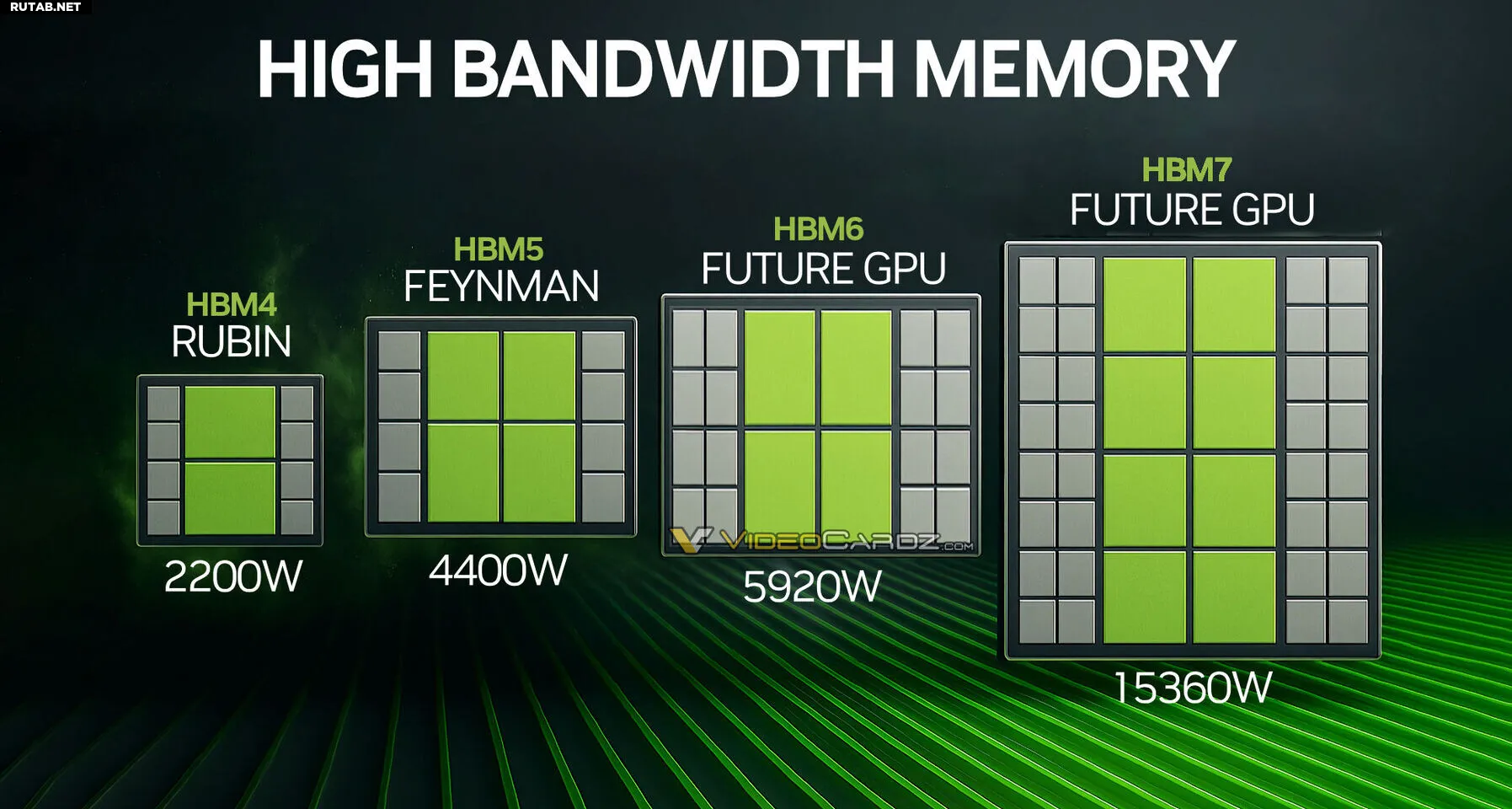

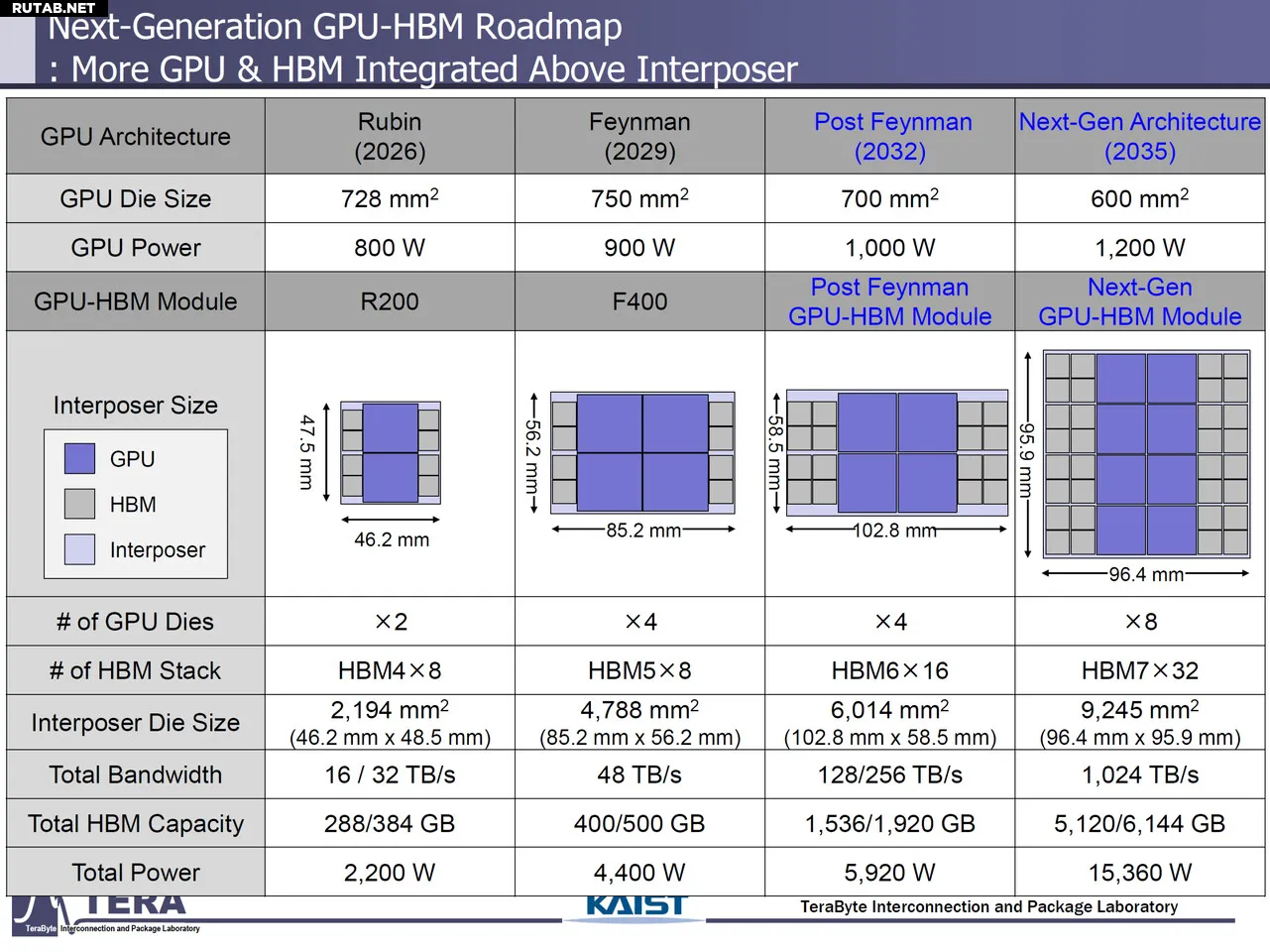

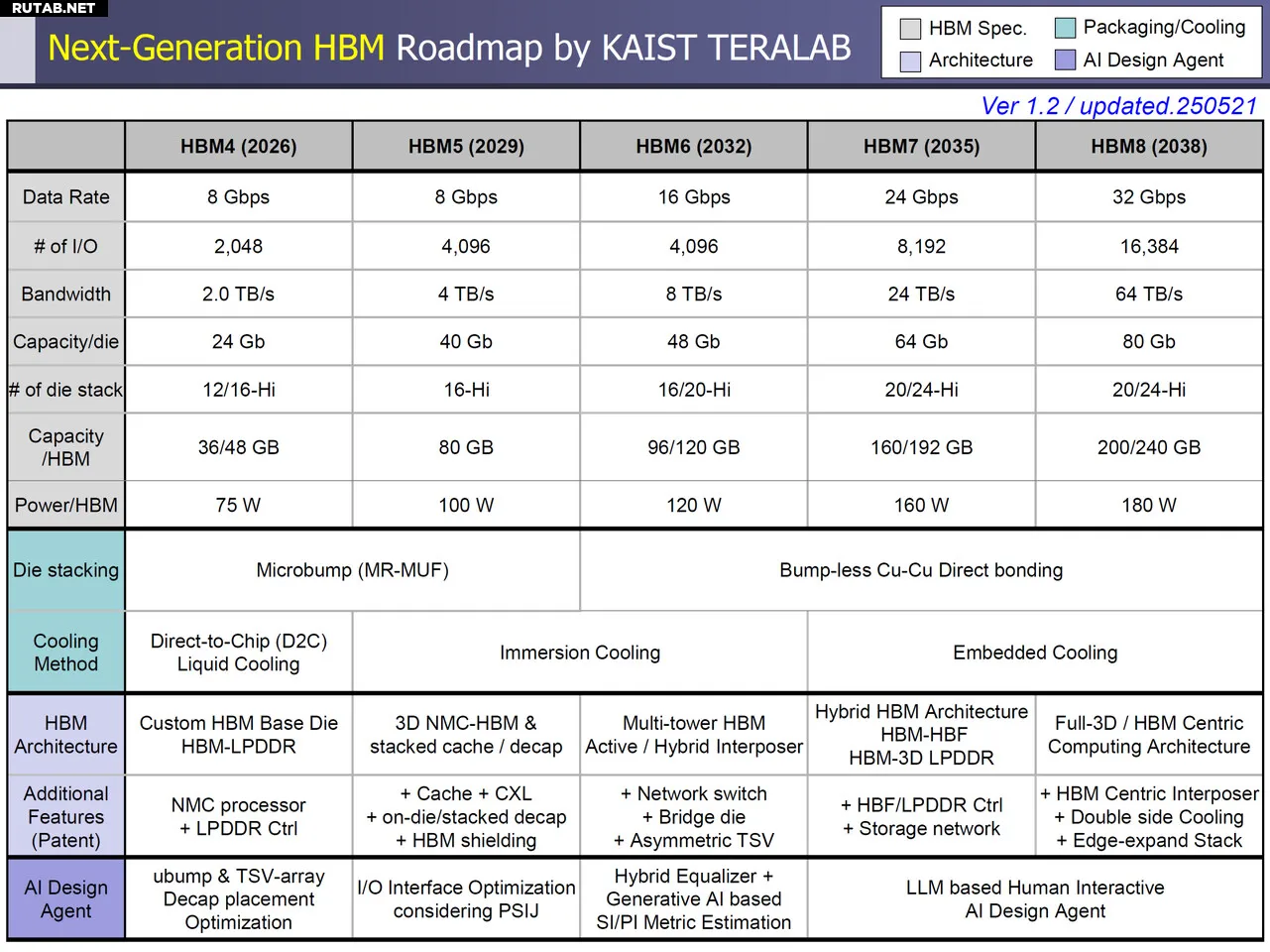

Первой станет HBM4, запланированная к выходу в 2026 году для ИИ-ускорителей и GPU для дата-центров. Она обеспечит пропускную способность около 2 ТБ/с на стек при скорости передачи данных 8 Гбит/с по 2048-битному интерфейсу. Количество слоев в стеке достигнет 12-16, что даст 36-48 ГБ на модуль при энергопотреблении 75 Вт. NVIDIA в своих будущих GPU серии Rubin и AMD в ускорителях Instinct MI500 планируют использовать HBM4, причем Rubin Ultra удвоит количество стеков памяти с 8 до 16, а AMD нацеливается на 432 ГБ на устройство.

К 2029 году появится HBM5, сохраняющая скорость 8 Гбит/с, но удваивающая количество линий ввода-вывода до 4096 бит, что повысит пропускную способность до 4 ТБ/с на стек. Энергопотребление вырастет до 100 Вт, а емкость достигнет 80 Гб при 16-слойных стеках с кристаллами по 40 Гбит. NVIDIA планирует выпустить ускоритель Feynman с HBM5, вмещающий 400-500 ГБ памяти в многокристальный модуль и потребляющий более 4400 Вт.

К 2032 году HBM6 удвоит скорость передачи до 16 Гбит/с и увеличит пропускную способность до 8 ТБ/с при 4096 линиях. Высота стека может достичь 20 слоев, обеспечивая до 120 ГБ на модуль при 120 Вт. Станут стандартом иммерсионное охлаждение и бесконтактная медь-медь связь.

Дорожная карта предсказывает появление HBM7 в 2035 году с 24 Гбит/с, 8192-битным интерфейсом, пропускной способностью 24 ТБ/с и до 192 ГБ на стек при 160 Вт. NVIDIA готовит ускоритель мощностью 15360 Вт для работы с этой монструозной памятью.

Завершит эволюцию HBM8 к 2038 году с 32 Гбит/с, 16384 линиями, 64 ТБ/с, стеками на 200-240 ГБ и встроенным охлаждением при 180 Вт. Помимо чистой DRAM, в брифинге упомянули гибридные архитектуры HBM-HBF (High-Bandwidth Flash), сочетающие NAND-память со стеками DRAM через сверхбыстрые сквозные кремниевые переходы для крупномасштабного ИИ-вывода.

С развитием ускорителей в сторону петабайтной пропускной способности и многокристальных конструкций эти новые стандарты HBM и HBF становятся единственным путем вперед.

Источник: Wccftech

0 комментариев