TSMC представила 2-нм техпроцесс: меньше энергопотребление или больше производительности

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

TSMC (аббревиатура от англ. Taiwan Semiconductor Manufacturing Company) — тайваньская компания, занимающаяся изучением и производством полупроводниковых изделий. Основана в 1987 году правительством Китайской республики и частными инвесторами.

Штаб-квартира TSMC находится в г. Википедия

Читайте также:Основатель TSMC говорит, что Intel должна сосредоточиться на искусственном интеллектеTSMC: годовой рост выручки — 34%, несмотря на замедлениеArm сократила рабочие места из-за ограничений TSMCПроцесс N2 от TSMC имеет большое преимущество перед 18A от Intel: плотность SRAMTSMC повысила производительность на 6% до 2 нм

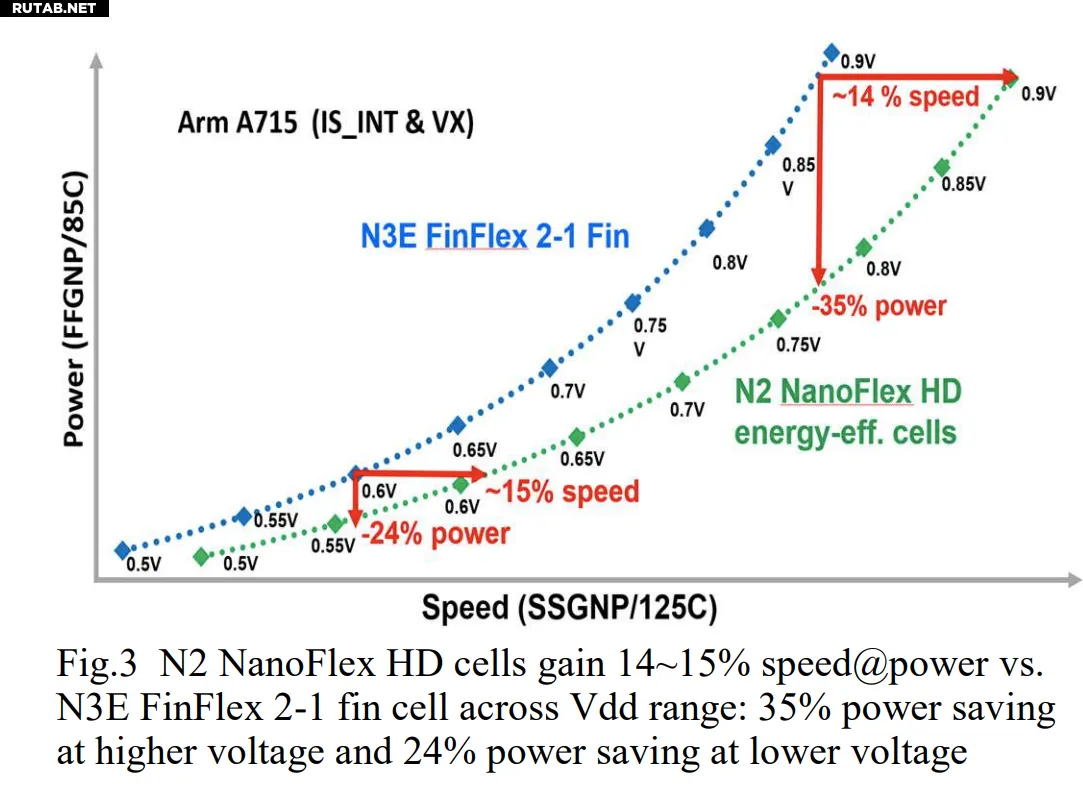

Gate-all-around nanosheet транзисторы позволяют разработчикам регулировать ширину канала для баланса производительности и энергоэффективности. Вдобавок к этому, N2 от TSMC добавляет N2 NanoFlex DTCO, что позволяет разработчикам разрабатывать короткие ячейки с минимальной площадью и повышенной энергоэффективностью или высокие ячейки, оптимизированные для максимальной производительности. Технология также включает шесть пороговых уровней напряжения (6-Vt), охватывающих диапазон 200 мВ, что достигается с помощью дипольной интеграции третьего поколения TSMC с диполями как n-типа, так и p-типа.

(Изображение предоставлено: TSMC через IEDM)

(Изображение предоставлено: TSMC через IEDM)

(Изображение предоставлено: TSMC через IEDM)

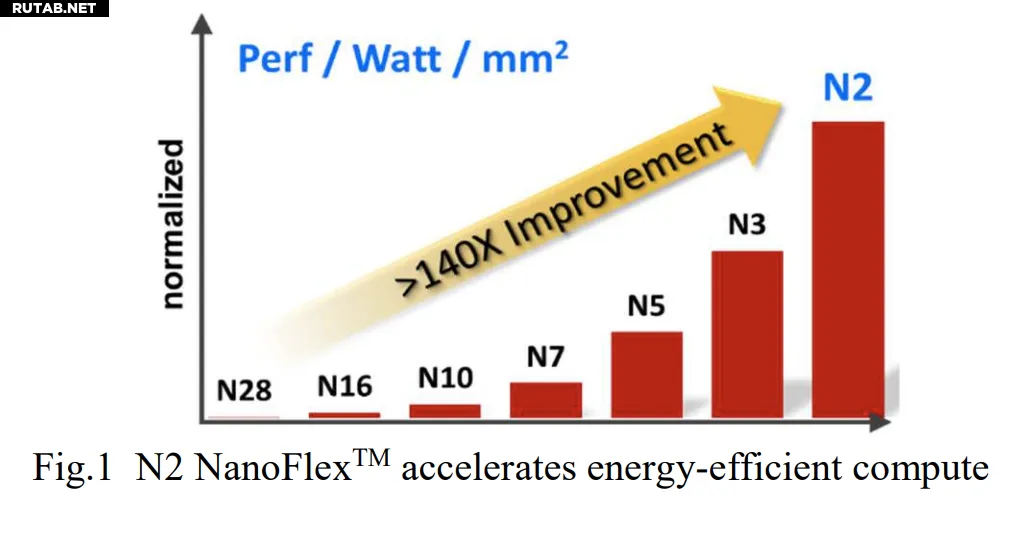

Инновации N2, представленные на уровне процесса и устройства, нацелены не только на повышение токов управления транзисторами за счет улучшения толщины листа, переходов, активации легирующих примесей и стресс-инжиниринга, но и на снижение эффективной емкости (Ceff) для достижения ведущей в своем классе энергоэффективности. В совокупности эти усовершенствования обеспечивают прирост скорости I/CV примерно на 70% и 110% для транзисторов нанолистов N-типа и P-типа соответственно.

По сравнению с FinFET транзисторы N2 nanosheet обеспечивают заметно лучшую производительность на ватт при низких диапазонах напряжения питания от 0,5 В до 0,6 В, где оптимизация процесса и устройства повышает тактовую частоту примерно на 20% и снижает энергопотребление в режиме ожидания примерно на 75% при работе с напряжением 0,5 В. Более того, интеграция N2 NanoFlex и опций с несколькими пороговыми напряжениями (multi-Vt) обеспечивает дополнительную гибкость проектирования для энергоэффективных процессоров с высокой плотностью логики.

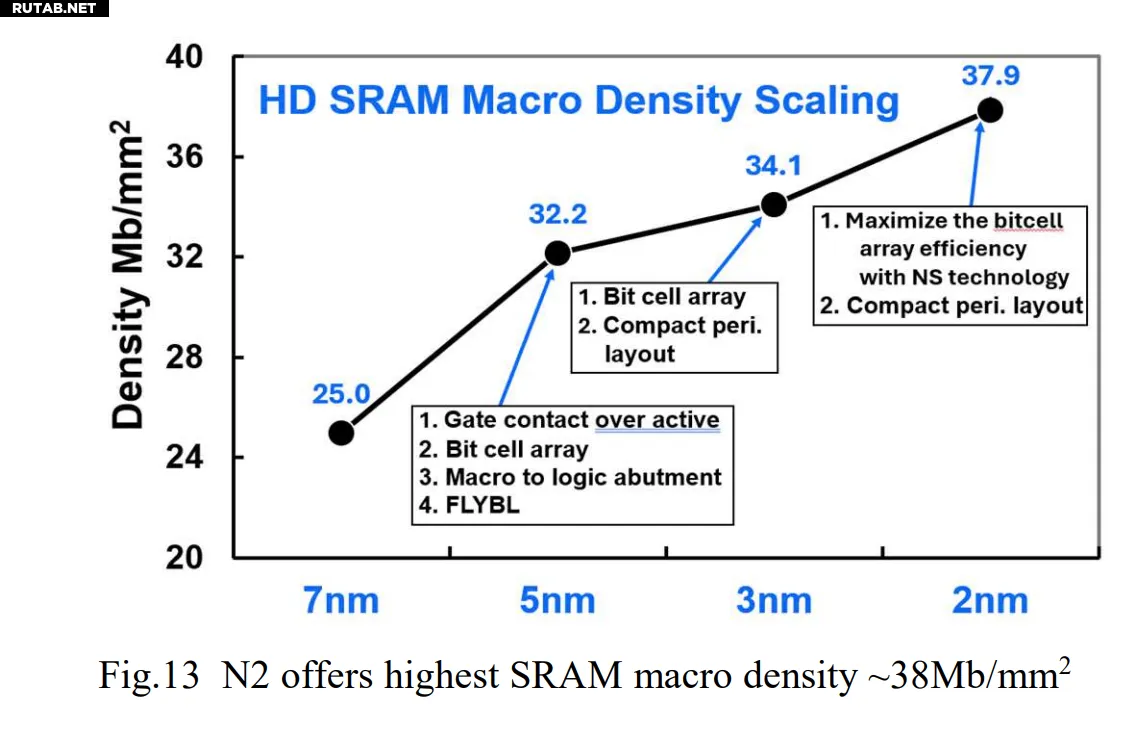

Преимущества транзисторной архитектуры и DTCO напрямую влияют на масштабируемость SRAM, чего было трудно достичь с передовыми узлами в последние годы. С N2 TSMC удалось достичь рекордной плотности SRAM 2 нм около 38 Мб/мм^2. В дополнение к достижению рекордной плотности SRAM, TSMC также снизила энергопотребление. Поскольку транзисторы GAA nanosheet имеют более жесткое изменение порогового напряжения (Vt-сигма), N2 достигает снижения минимального рабочего напряжения (Vmin) примерно на 20 мВ для макросов High Current (HC) и снижения на 30–35 мВ для макросов High Density (HD) по сравнению с конструкциями на основе FinFET. Эти улучшения обеспечивают стабильную функциональность чтения и записи SRAM примерно до 0,4 В, сохраняя при этом высокую производительность и надежность.

Кроме того, дополнительные функции N2 для приложений HPC включают сверхвысокопроизводительные конденсаторы MiM ( SHP-MiM), обеспечивающие емкость около 200 фФ/мм², что помогает достичь более высоких максимальных рабочих частот (Fmax) за счет снижения переходного падения напряжения.

Наконец, технология N2 от TSMC включает новую опцию Cu RDL с плоской пассивацией и TSV, которая оптимизирована для 3D-укладки «лицом к лицу» и «лицом к спине» с шагом связей SoIC 4,5 мкм, что, по словам TSMC, должно стать полезной функцией для ИИ, HPC и даже мобильных устройств.

Компания TSMC планирует начать производство по технологии N2 во второй половине 2025 года.

Источник: Tomshardware.com

0 комментариев