Cadence представила первую в отрасли память LPDDR6/5X с пропускной способностью 14,4 Гбит/с для ИИ-инфраструктуры

Компания Cadence объявила о выпуске первой в отрасли системы IP-ядер памяти LPDDR6/5X, оптимизированной для работы на скорости до 14,4 Гбит/с — это на 50% быстрее, чем у предыдущего поколения LPDDR DRAM. Новое решение станет ключевым элементом для масштабирования ИИ-инфраструктуры, удовлетворяя растущие требования к пропускной способности и объёму памяти для следующего поколения больших языковых моделей (LLM), агентного ИИ и других ресурсоёмких задач в различных отраслях. Уже ведутся переговоры с ведущими компаниями в области ИИ, высокопроизводительных вычислений (HPC) и центров обработки данных.

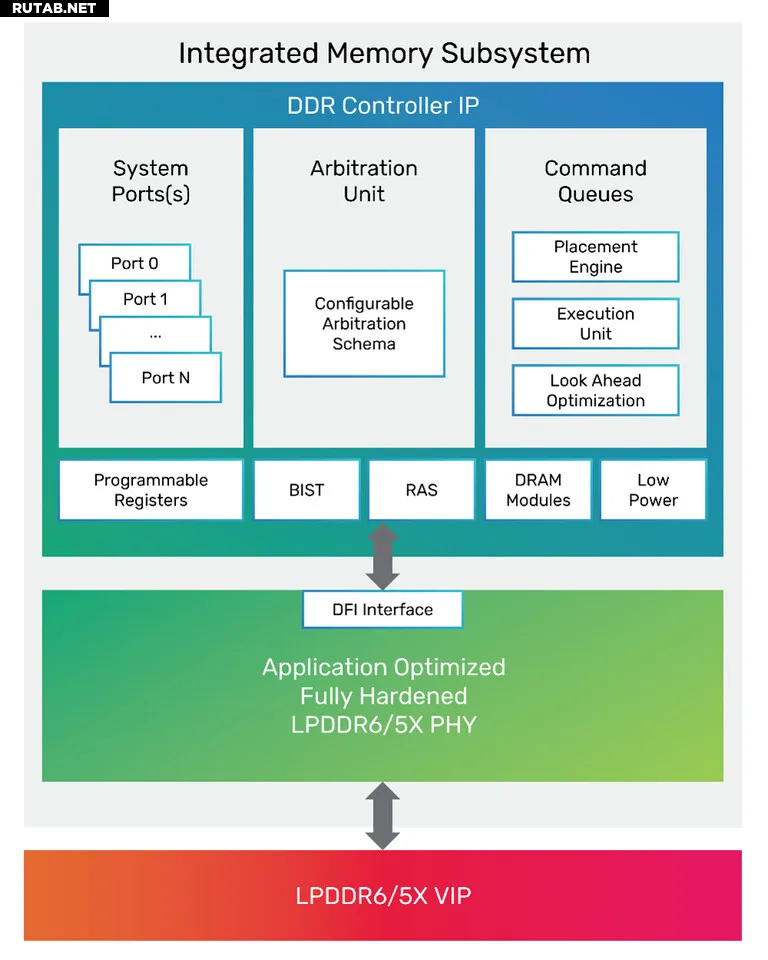

IP-решение Cadence для стандарта JEDEC LPDDR6/5X включает передовую архитектуру PHY и высокопроизводительный контроллер, разработанные для максимальной эффективности по мощности, производительности и площади (PPA). Оно поддерживает как протоколы LPDDR6, так и LPDDR5X, обеспечивая гибкость интеграции в традиционные монолитные SoC, а также в многокристальные системы благодаря фреймворку Cadence для чиплетов. Этот фреймворк, включая предыдущее поколение LPDDR, был успешно реализован в 2024 году.

«Эволюция центров обработки данных от виртуализации HPC-вычислений к масштабному обучению и выводу ИИ привела к активному развитию ИИ-инфраструктуры, и проектирование эффективных интерфейсов памяти стало как никогда важным. LPDDR6 стал ключевым элементом для ускоренных вычислений, обеспечивая скорость, пропускную способность, энергопотребление и объём, необходимые для эффективного выполнения ИИ-инференции», — заявил Бойд Фелпс, старший вице-президент и генеральный менеджер группы Silicon Solutions в Cadence. «С этим релизом Cadence продолжает лидерство в области IP-ядер памяти, предлагая первую в отрасли реализацию LPDDR6 в виде оптимизированной подсистемы для приложений заказчиков».

Полная система памяти, включающая PHY и контроллер, основана на новой высокопроизводительной, масштабируемой и адаптируемой архитектуре, развивающей успешные линейки DDR5 12,8 Гбит/с, LPDDR5X 10,7 Гбит/с и GDDR7-36G. Это первое предложение в новой линейке IP-ядер LPDDR6 от Cadence поддерживает стандарты LPDDR6 и LPDDR5X, включая LPDDR5X CAMM2.

Решение подходит для рынков ИИ, мобильных устройств, потребительской электроники, корпоративных HPC-систем и облачных ЦОД, обеспечивая гибкость для конечных продуктов с различными требованиями к производительности, объёму памяти и стоимости. PHY LPDDR6/5X можно настраивать под разные топологии корпусов и систем, а также использовать в виде готового макроса для быстрой интеграции и сокращения времени вывода на рынок.

Контроллер Cadence LPDDR6/5X включает полный набор стандартных и передовых функций для интерфейсов памяти, таких как поддержка шины Arm AMBA AXI. Контроллер поставляется в виде мягкого RTL-макроса для максимальной гибкости в настройке характеристик, энергопотребления, площади и производительности.

Решение также включает модель памяти LPDDR6, позволяющую инженерам проводить комплексную верификацию и гарантировать совместимость проектов SoC с последним стандартом JEDEC. Модель содержит полный набор проверок протокола, функционального покрытия и план верификации.

Новое IP-ядро LPDDR6/5X уже доступно для заказчиков и дополняет семейство решений Cadence для памяти, включающее DDR, GDDR и HBM. Оно разработано с использованием передовых инструментов проектирования аналоговых и смешанных сигналов компании. В сочетании с чиплет-фреймворком Cadence на базе UCIe, новое решение ускоряет реализацию чиплетов.

0 комментариев