Qualitas Semiconductor разрабатывает первый собственный PCIe 6.0 PHY IP

PCI Express (Peripheral Component Interconnect Express), или PCIe, или PCI-e (также известная как 3GIO for 3rd Generation I/O; не путать с PCI-X и PXI) — компьютерная шина (хотя на физическом уровне шиной не является, будучи соединением типа «точка-точка»), использующая программную модель шины PCI и высокопроизводительный физический протокол, основанный на последовательной передаче данных.

Разработка стандарта PCI Express была начата фирмой Intel после отказа от шины InfiniBand. Официально первая базовая спецификация PCI Express появилась в июле 2002 года.

Развитием стандарта PCI Express занимается организация PCI Special Interest Group. Википедия

PCI Express (Peripheral Component Interconnect Express), или PCIe, или PCI-e (также известная как 3GIO for 3rd Generation I/O; не путать с PCI-X и PXI) — компьютерная шина (хотя на физическом уровне шиной не является, будучи соединением типа «точка-точка»), использующая программную модель шины PCI и высокопроизводительный физический протокол, основанный на последовательной передаче данных.

Разработка стандарта PCI Express была начата фирмой Intel после отказа от шины InfiniBand. Официально первая базовая спецификация PCI Express появилась в июле 2002 года.

Развитием стандарта PCI Express занимается организация PCI Special Interest Group. Википедия

Читайте также:Графические процессоры используют память накопителей PCIeУтечка диаграммы чипсета Intel Arrow Lake показывает больше линий PCIe, без поддержки DDR4SK hynix вступает в ряды AI со своим первым твердотельным накопителем PCIe 5.0Оптическое соединение PCIe 7.0 достигает невероятных 128 ГТ/сПроблема с соблюдением требований PCIe 6.0 и 7.0

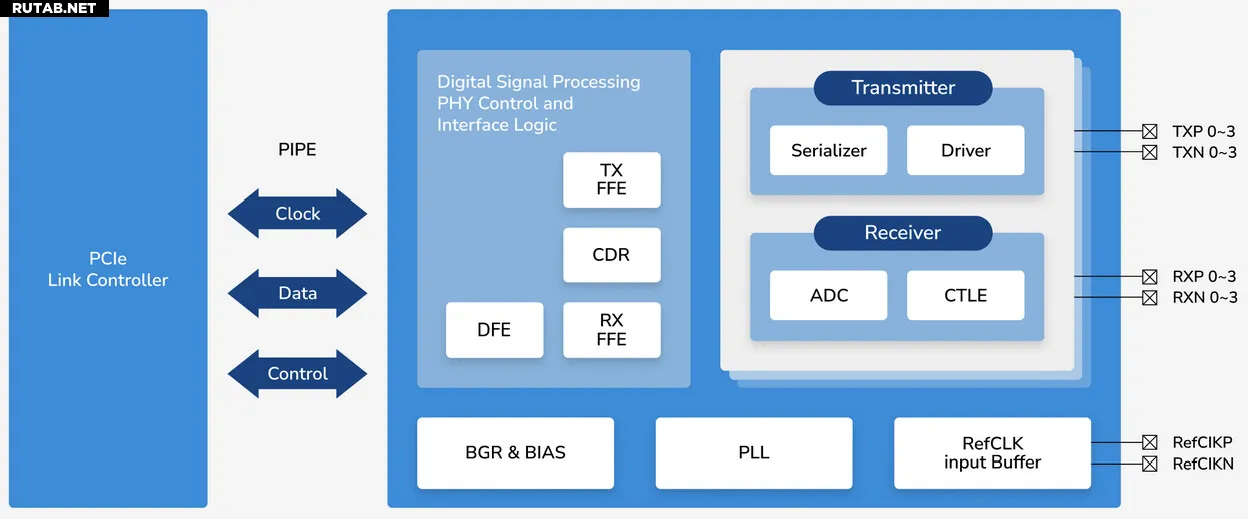

PCIe 6.0 PHY IP может достигать скорости передачи до 64 ГТ/с на полосу. При использовании всех 16 линий он может передавать данные со скоростью до 256 ГБ/с. Эти скорости делают его хорошо подходящим для центров обработки данных и технологий беспилотных автомобилей, где важна быстрая обработка данных. Qualitas добилась таких результатов за счет внедрения технологии сигнализации 100G PAM4. Подчеркнув важность нового IP, генеральный директор Qualitas д-р Духо Ким сообщил о намерении компании продолжать расширять границы полупроводниковых технологий.

Key Features

- Улучшенная технология КМОП-устройств с низким энергопотреблением, изготовленная по 5-нм техпроцессу

- 1,8 В ± 5 %, 0,85 В ± 5 %, двойной источник питания

- Соответствует спецификациям PCIe Base 6.0 и PIPE 6.1.

- Поддержка Gen 1, Gen 2, Gen 3, Gen 4, Gen 5 и Gen 6.

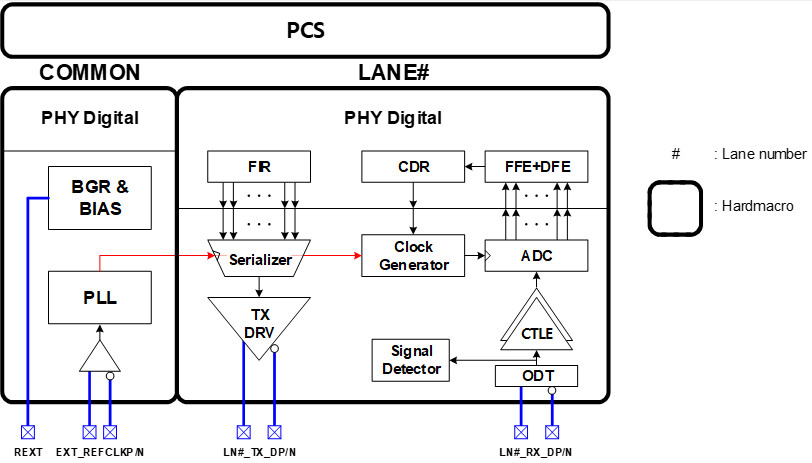

- Конфигурация каналов для линий данных

- Общий (CMN) и 1, 2 или 4 канала передачи данных

- Поддержка следующих уровней предыскажения передатчика

- -3,5/-6 дБ для Gen 1 и Gen 2

- Multi-Tap FIR с разрешением 1/63 для поколений от 3 до 6

- Поддержка CTLE, многоточечного FFE на основе DSP и одноточечного DFE для выравнивания каналов в приемнике.

- Поддержка адаптивного выравнивания канала

- Требуется опорная частота 100 МГц (поддержка дифференциального входного буфера)

- Встроенная функция самотестирования, позволяющая генерировать и проверять шаблоны PRBS.

- ПК включены в хард-макрос PHY

Источник: Design&Reuse

0 комментариев