PCI-SIG представила черновик спецификации PCIe 8.0: пропускная способность до 1 ТБ/с и новый разъём

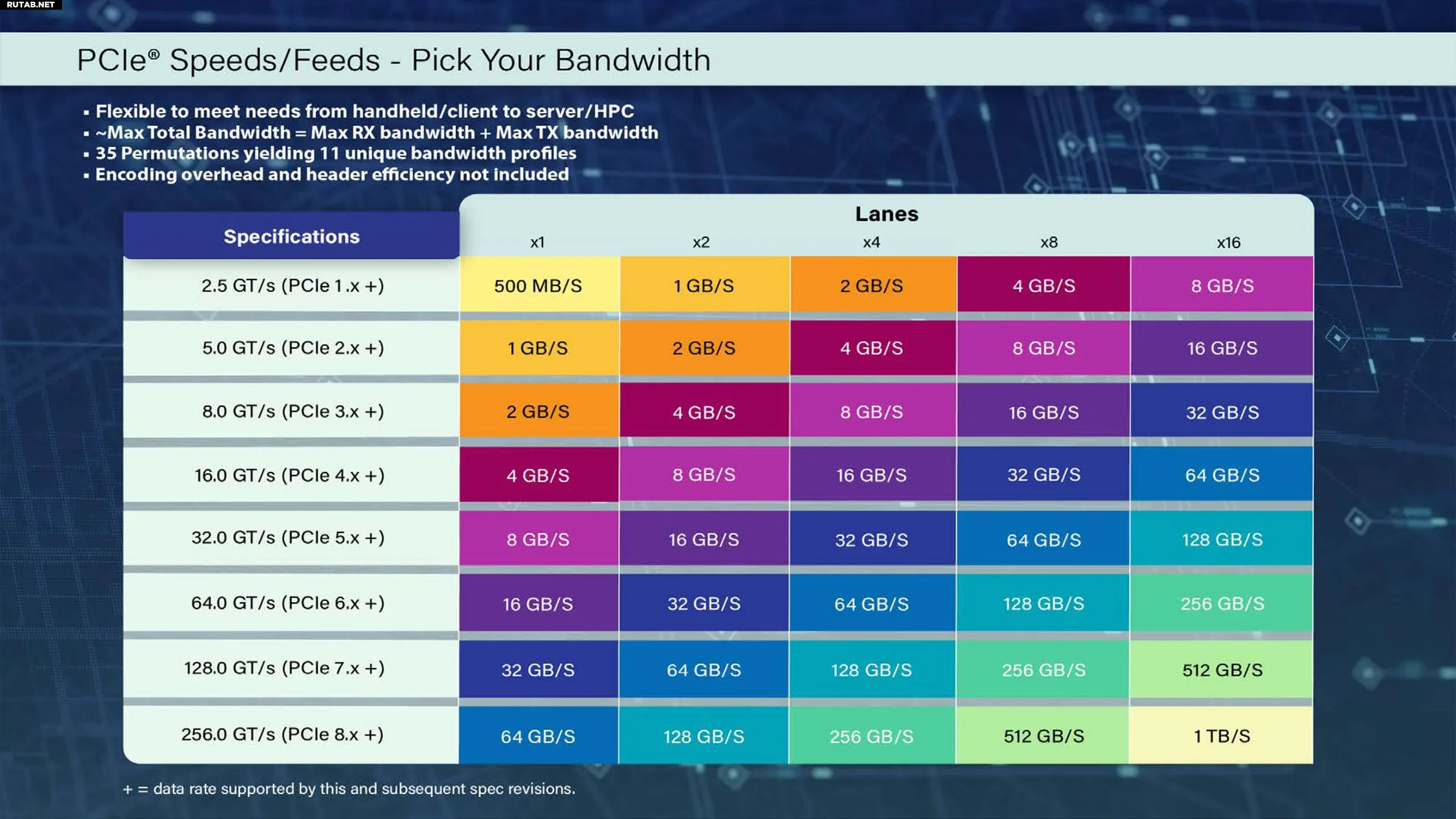

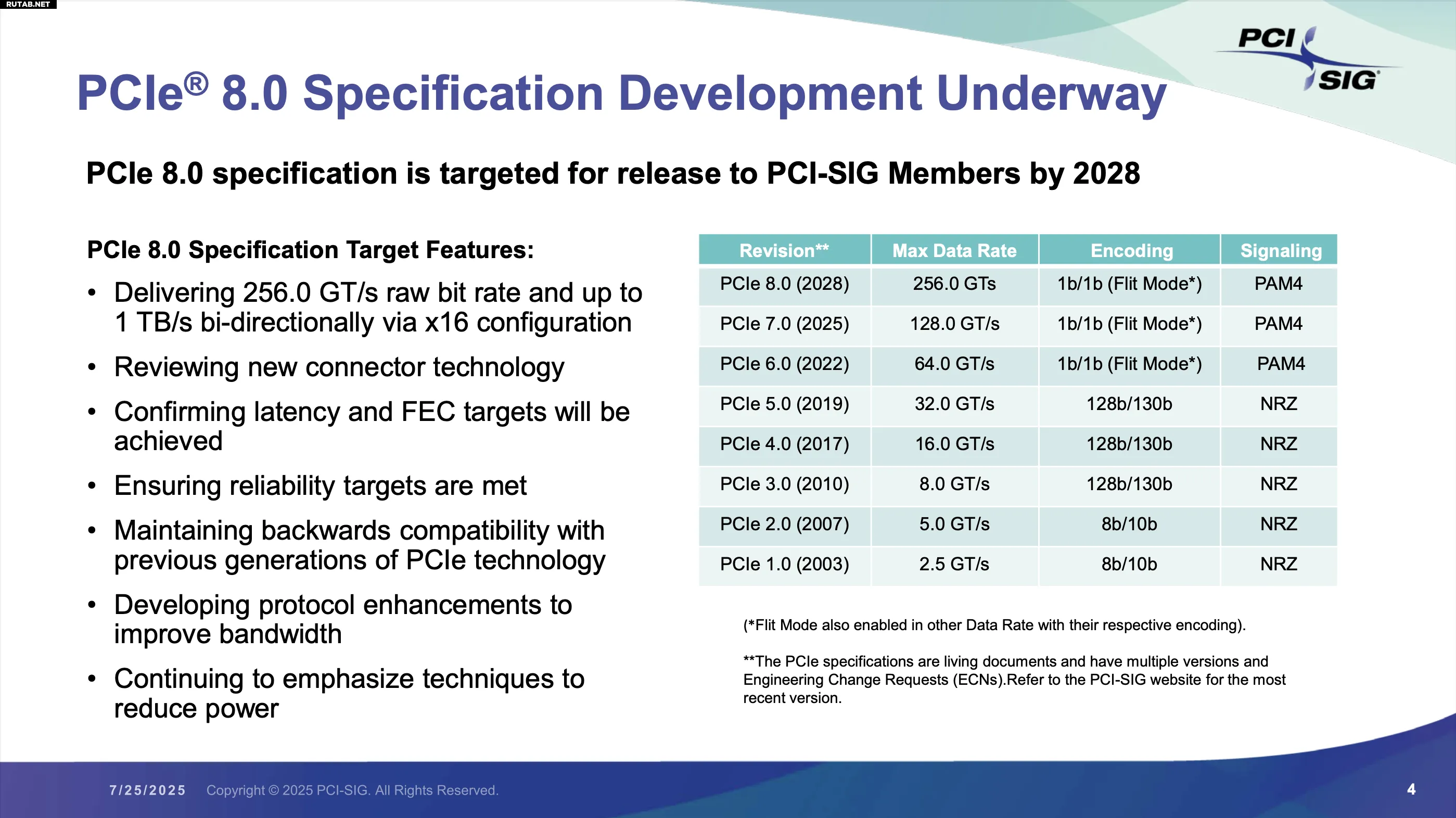

Организация PCI-SIG, курирующая развитие стандарта PCIe, объявила о выпуске первой черновой версии спецификации PCIe 8.0 (ревизия 0.5). Этот документ фиксирует ключевые архитектурные требования и позволяет участникам консорциума начать раннее прототипирование и подготовку окончательных предложений. Версия 0.5 подтверждает, что скорость передачи данных по новой шине достигнет 256 GT/с, что обеспечит двунаправленную пропускную способность до 1 ТБ/с в конфигурации x16.

Ревизия 0.5 — это первый полноценный черновик стандарта, который закрепляет основные концептуальные цели и механизмы. В документе описаны все ключевые аспекты архитектуры: электрические, логические, вопросы совместимости и программного обеспечения. Это означает, что PCI-SIG сохраняет целевую скорость в 256 GT/с, использование модуляции PAM4 с прямым исправлением ошибок (FEC) и кодированием Flit Mode, улучшения протокола для повышения пропускной способности, обратную совместимость, а также изучает новую технологию разъёмов. Поскольку версия 0.5 не является финальной, некоторые электрические параметры и оптимизации протокола могут быть скорректированы.

Этот этап — важная веха, так как теперь разработчики оборудования, включая крупные компании, такие как AMD, Intel и Nvidia, а также производители IP-блоков и PHY, могут приступить к раннему прототипированию и архитектурной работе. Важно, что спецификация уже достаточно зрелая, и разработка может начинаться.

Изображение: PCI-SIG

Одной из интригующих деталей анонса является то, что PCI-SIG продолжает оценивать новую технологию разъёмов. Это означает, что современный медный физический уровень приближается к пределу своих возможностей.

Бюджет потерь, перекрёстные помехи и отражения сигнала уже стали серьёзными ограничениями для PCIe 5.0 и 6.0. Однако для PCIe 8.0 с его скоростью 256 GT/с — показателем, которого ещё не достигал ни один медный стандарт, — эти проблемы, вероятно, превратятся в настоящий кошмар. На таких скоростях традиционный краевой разъём и разводка на материнской плате могут не обеспечить приемлемую целостность сигнала без чрезмерного энергопотребления (для выравнивания) или задержек (для FEC). В связи с этим PCI-SIG может рассмотреть возможность перепроектировки слотов PCIe с использованием лучших материалов и более жёстких допусков, либо снова сократить электрические пути, увеличив количество редрайверов на линию. В любом случае, учитывая желание PCI-SIG сохранить обратную совместимость, кардинальных изменений на уровне разъёмов ожидать не стоит.

С выходом этого черновика стандарт PCIe 8.0 продолжает движение к финальной ратификации, запланированной на 2028 год.

Источник: Tomshardware.com

0 комментариев