ИИ-агент спроектировал полноценный процессор RISC-V за 12 часов по текстовому описанию из 219 слов

Стартап по проектированию чипов с помощью ИИ Verkor.io заявил, что его агентная система Design Conductor автономно создала полноценное ядро процессора RISC-V. Система взяла документ с требованиями объемом 219 слов и за 12 часов сгенерировала верифицированный проект, готовый к производству. Это на порядки быстрее стандартных 18–36 месяцев, которые обычно занимает коммерческая разработка чипов.

Изображение: Microsoft

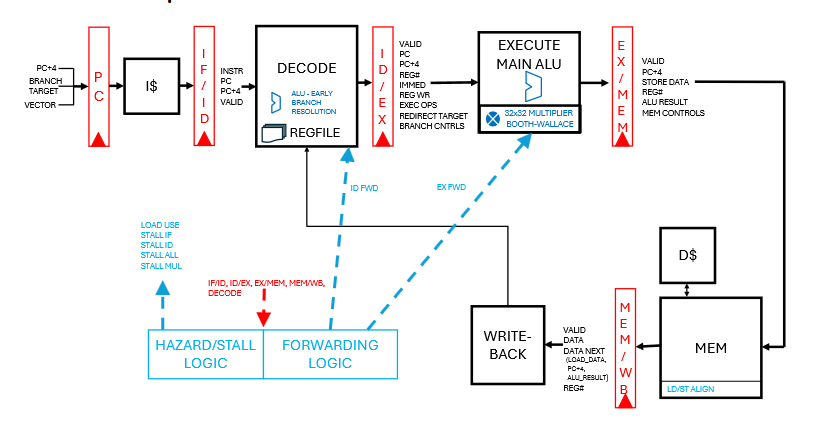

По словам Verkor, это первый случай, когда автономный агент построил рабочий процессор от спецификации до файла компоновки GDSII. Получившийся процессор, названный VerCore, представляет собой ядро с пятиступенчатым конвейером, последовательным выполнением и одним потоком команд. Он достиг тактовой частоты 1,48 ГГц на технологическом процессе ASAP7 (7 нм) и набрал 3261 балл в тесте CoreMark.

В документе Verkor подробно описывается архитектура конвейера, включающая этапы выборки, декодирования, выполнения, обращения к памяти и обратной записи, с ранним разрешением ветвлений и пересылкой операндов. В ходе оптимизации система самостоятельно реализовала быстрый умножитель Бута-Уоллеса с частотой 2,57 ГГц и выбрала конструкцию с штрафом за ветвление в один такт после тестирования вариантов с одним и двумя тактами. Производительность VerCore сравнивается с Intel Celeron SU2300, мобильным чипом 2011 года на архитектуре Penryn.

Пятиступенчатое ядро без кэша и внеочередного выполнения — довольно простая конструкция по отраслевым меркам. В самой статье Verkor отмечается, что разработка передовых чипов стоит более 400 миллионов долларов (~32 млрд рублей) и занимает 18–36 месяцев с участием сотен инженеров. VerCore гораздо проще, но 12-часовой срок все равно примечателен для полностью автономной работы от спецификации до компоновки, даже если на этом относительно низком уровне сложности потребовались «многие десятки миллиардов токенов».

Изображение: Verkor.io

VerCore не был физически изготовлен и верифицировался только в симуляции с помощью Spike (эталонный симулятор ISA RISC-V). ASAP7 — это академический набор средств проектирования, а не производственный 7-нм техпроцесс. Verkor утверждает, что в симуляции может запустить вариант uCLinux.

Авторы работы честно признают ограничения языковых моделей: агент иногда «недооценивает сложность работы, необходимой для решения определенных проблем». Например, при нарушении временных характеристик Design Conductor пытался кардинально «углубить конвейер» вместо поиска более простых решений. В другом случае модель рассуждала о Verilog (языке описания аппаратуры, управляемом событиями) так, как если бы это был последовательный код. Исследователи подсчитали, что для доведения системы до готового к производству чипа все еще потребуется от пяти до десяти экспертов-людей. Кроме того, требования к вычислительным мощностям растут нелинейно с увеличением сложности проекта, что делает процесс менее практичным в коммерческих масштабах. Verkor планирует выпустить исходный код VerCore (RTL) и скрипты сборки к концу апреля, а также продемонстрировать реализацию на ПЛИС на конференции DAC.

Источник: Tomshardware.com

0 комментариев