Intel представила огромный тестовый процессор для ИИ с четырьмя логическими чиплетами и 12 стеками HBM4

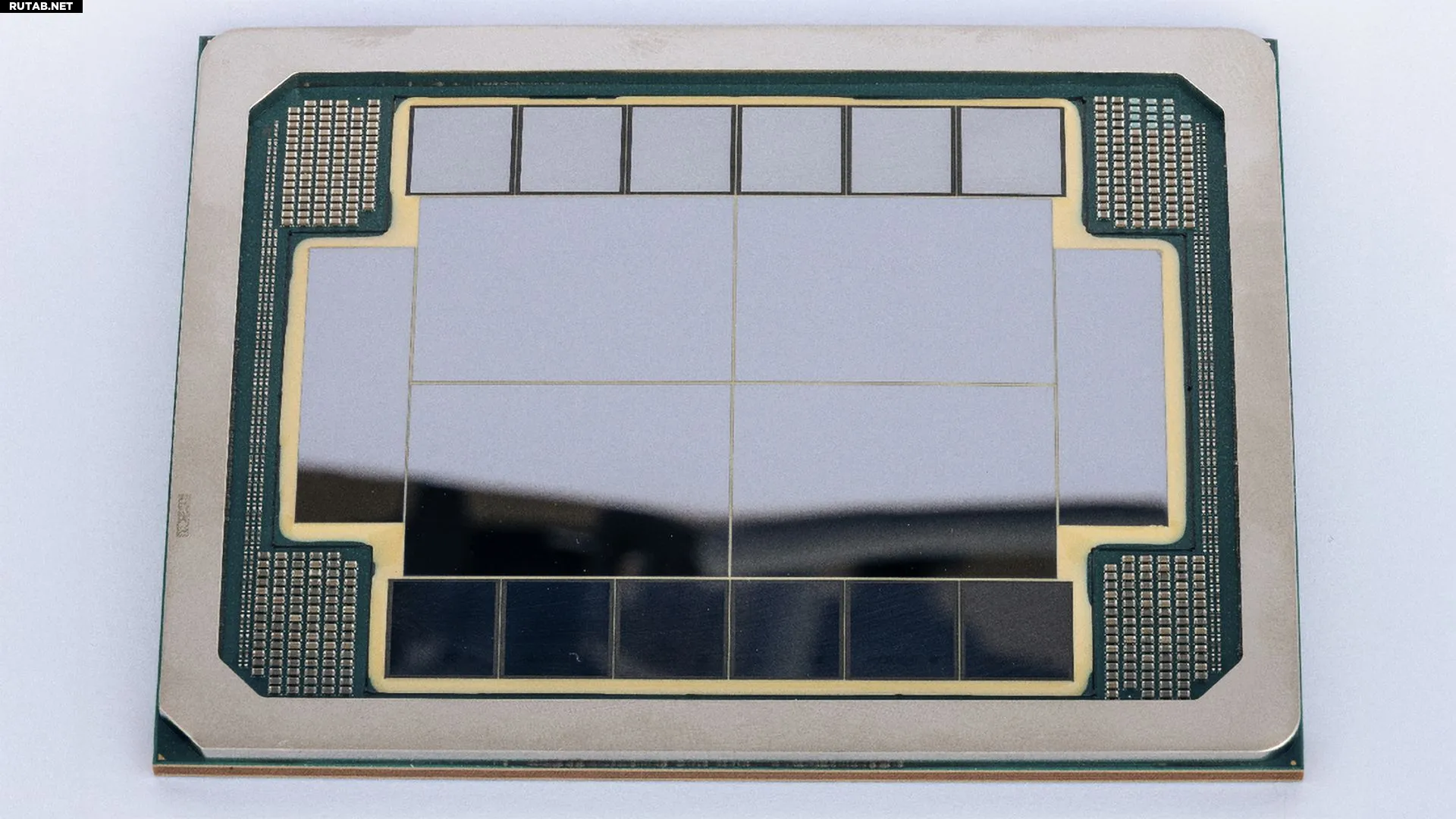

Подразделение Intel Foundry на этой неделе опубликовало рекламный документ, демонстрирующий свои передовые технологии для систем искусственного интеллекта и высокопроизводительных вычислений. В нём компания показала «тестовый образец ИИ-чипа», который наглядно демонстрирует её текущие возможности в области упаковки чипов. Конструкция впечатляет: это система в корпусе (SiP) размером в 8 ретикул, содержащая четыре логических чиплета, 12 стеков памяти HBM4 и два I/O-чиплета. В отличие от концепта с 16 логическими чиплетами и 24 стеками HBM5, представленного месяцем ранее, эта система уже может быть изготовлена.

Важно отметить, что Intel демонстрирует не готовый к работе ИИ-ускоритель, а именно тестовый образец, показывающий, как физически могут быть собраны будущие процессоры для ИИ и HPC. По сути, компания представляет весь свой метод построения, который объединяет крупные вычислительные чиплеты, стеки высокоскоростной памяти, сверхбыстрые межчиповые соединения и новую систему подачи питания в одном производимом корпусе. Этот подход существенно отличается от предложений TSMC.

В основе платформы лежат четыре крупных логических чиплета, предположительно изготовленных по технологии Intel 18A (с транзисторами RibbonFET и обратной разводкой питания PowerVia). Они окружены стеками памяти HBM4 и I/O-чиплетами и соединены с помощью 2.5D мостов EMIB-T, встроенных прямо в подложку корпуса. EMIB-T использует сквозные кремниевые переходы, что позволяет передавать питание и сигналы как по вертикали, так и по горизонтали, максимизируя плотность соединений. Для связи между чиплетами используется интерфейс UCIe со скоростью 32 GT/s и выше.

Изображение: Intel

Тестовый образец также демонстрирует движение Intel в сторону вертикальной интеграции. Дорожная карта компании включает процесс Intel 18A-PT, разработанный специально для чиплетов, на которые можно накладывать другие логические кристаллы или память. Для вертикального соединения чиплетов Intel использует технологии упаковки семейства Foveros, которые обеспечивают сверхплотную медь-медную стыковку. Вместе с мостами EMIB это позволяет Intel создавать гибридные сборки — альтернативу крупным кремниевым интерпозерам с более высоким выходом годных пластин.

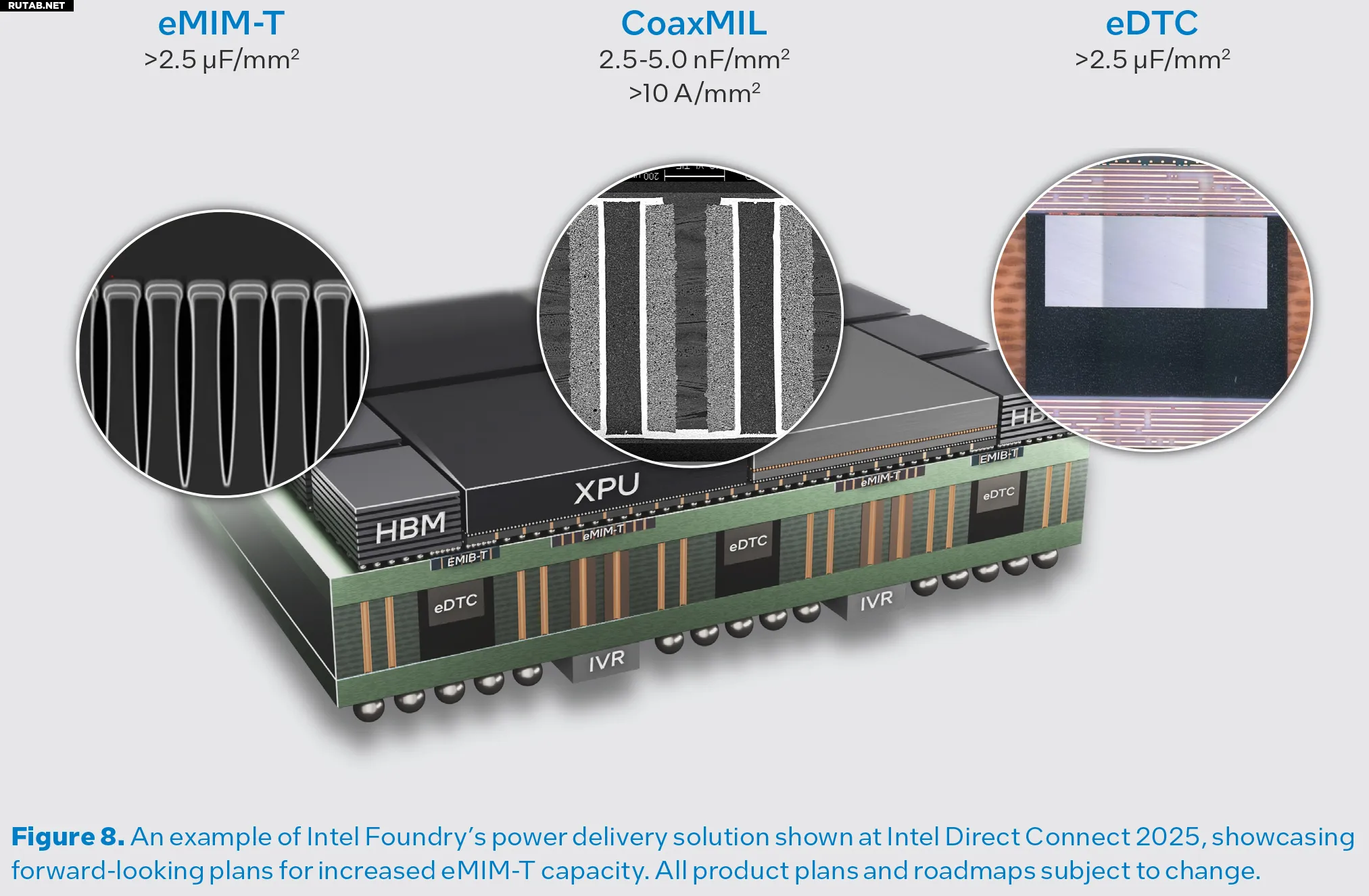

Для многокристальных ускорителей ИИ и HPC ключевым ограничением является подача питания. Платформа Intel должна объединять все последние инновации компании в этой области: PowerVia, конденсаторы Omni MIM на кристалле, развязку на уровне мостов в EMIB-T, а также встроенные индукторы CoaxMIL. Это поддерживает работу «полуинтегрированных» стабилизаторов напряжения, расположенных под каждым стеком и под самим корпусом. Такая многослойная сеть предназначена для поддержки резких скачков тока в генеративных ИИ-задачах без просадок напряжения.

Демонстрация «тестового образца ИИ-чипа» — это способ Intel привлечь заказчиков. Остаётся вопрос, будет ли архитектура, показанная сегодня, использована в будущем ИИ-ускорителе компании под кодовым названием Jaguar Shores, выход которого запланирован на 2027 год.

Источник: Tomshardware.com

0 комментариев