AMD готовит революцию в Zen 6: переход на новые D2D-соединения для повышения энергоэффективности и снижения задержек

Сообщается, что AMD планирует внедрить совершенно новую технологию соединений D2D (die-to-die) в процессорах следующего поколения Zen 6, которая заменит существующую технологию SERDES. Первые признаки этих изменений уже можно увидеть в APU Strix Halo.

Начиная с архитектуры Zen 2, AMD использовала технологию SERDES PHY для соединений между чиплетами CCD. Однако с развитием технологий и ростом требований существующий метод соединения постепенно начинает показывать свои ограничения.

SERDES означает «сериализатор/десериализатор». Эта технология в основном используется для преобразования параллельного трафика от различных CCD в последовательный битовый поток и передачи его между чипами, после чего десериализатор преобразует последовательный поток данных обратно.

Этот подход имеет два основных недостатка: процесс сериализации и десериализации требует энергии для восстановления тактовой частоты, выравнивания и кодирования/декодирования. Кроме того, преобразование потока данных увеличивает задержку связи между чипами, что является основным недостатком существующей технологии.

С добавлением новых функций, таких как NPU, AMD требуется более стабильная и менее затратная пропускная способность для соединения памяти и CCD. В APU Strix Halo AMD уже внесла значительные улучшения, которые могут указывать на будущее направление развития процессоров Zen 6.

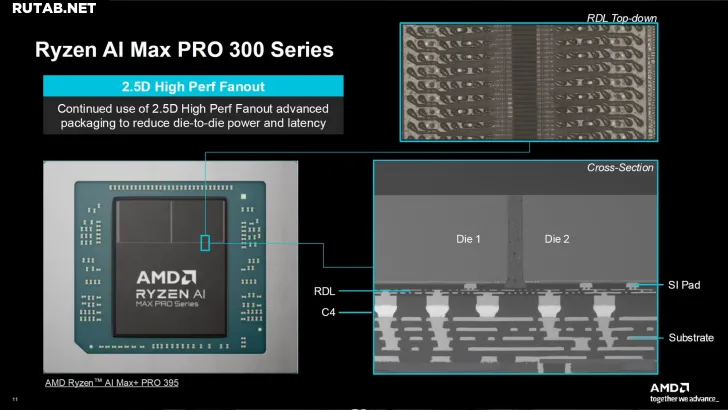

Конкретно, AMD с помощью RDL (слоя перераспределения) проложила множество коротких и тонких параллельных линий между чипами. Эти линии расположены в «интерпозере» под чипом.

Благодаря технологии InFO-oS (Integrated Fan-Out on Substrate) от TSMC, линии прокладываются между кремниевым чипом и органической подложкой, что позволяет архитектуре CPU общаться через широкие параллельные порты.

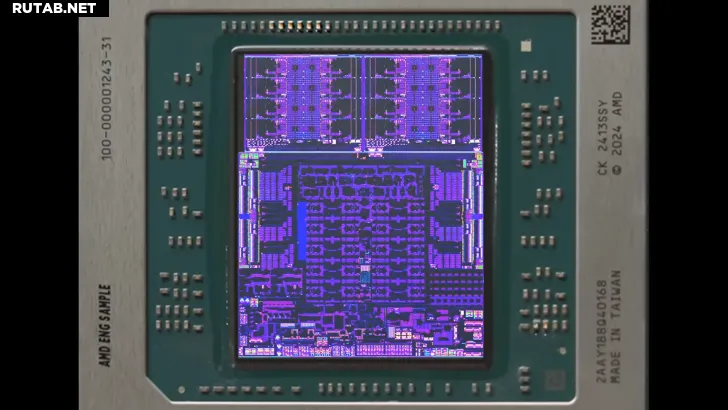

Аналитики High Yield, изучив дизайн чипа Strix Halo, обнаружили этот новый метод. На чипе Strix Halo есть небольшая прямоугольная область прокладок, что является классическим проявлением технологии InFO-oS, в то время как исходный большой модуль «SERDES» был удален.

Этот новый способ соединения D2D значительно снижает энергопотребление и задержки, поскольку больше не требуется процессов сериализации и десериализации. Что еще более важно, за счет увеличения количества портов в архитектуре CPU общая пропускная способность значительно возрастает.

Однако этот метод также привносит сложности в проектирование, особенно при разработке многослойных RDL, и требует изменения приоритетов разводки, поскольку пространство под чипом используется для трассировки финального вывода.

ИИ: Этот переход AMD выглядит логичным шагом в эволюции чиплетной архитектуры. Снижение задержек и энергопотребления межчиплетных соединений критически важно для будущих процессоров с большим количеством ядер и интегрированными NPU. Технология, опробованная в Strix Halo, судя по всему, станет основой для следующего большого скачка производительности Zen 6.

0 комментариев