Ядра процессоров AMD Strix Point SoC «Zen 5» и «Zen 5c» имеют 256-битные пути передачи данных FPU

Advanced Micro Devices, Inc. (AMD, дословный перевод с англ. — «передовые микроустройства») — производитель интегральной микросхемной электроники. Второй по объему производства и продаж производитель процессоров архитектуры x86 c долей рынка 16,9 %▲(2014), а также один из крупнейших производителей графических процессоров (после приобретения ATI Technologies в 2006 году), чипсетов для материнских плат и флеш-памяти. Компания с 2009 года не имеет собственного производства и размещает заказы на мощностях других компаний. Википедия

Читайте также:AMD немного подробно описывает iGPU Radeon 890M RDNA 3.5 «Strix Point»Подробнее о MCM AMD «Granite Ridge»: CCD построен на N4P, cIOD перенесенIntel i9 13 и 14 поколения часто отказывают. Компания переходит на AMDСупервизор Unreal Engine отметил отказы чипов Intel в 50% случаевНовый измеритель задержки кадров от AMD

Читайте также:Старый игровой флагман AMD Zen 4 превосходит Zen 5 в новых игровых тестах12-ядерный процессор Zen 5 превзошел 20-ядерный процессор Intel и Apple M3 Max в PassMarkНовый чип Ryzen AI 7 Pro 160 превосходит предыдущее поколение Ryzen 9Ранние тесты процессоров Zen 5 подтверждают заявления AMD о IPCПредставлен Ryzen 9000. Вот новые процессоры Zen 5, но AMD не предоставила важной информации

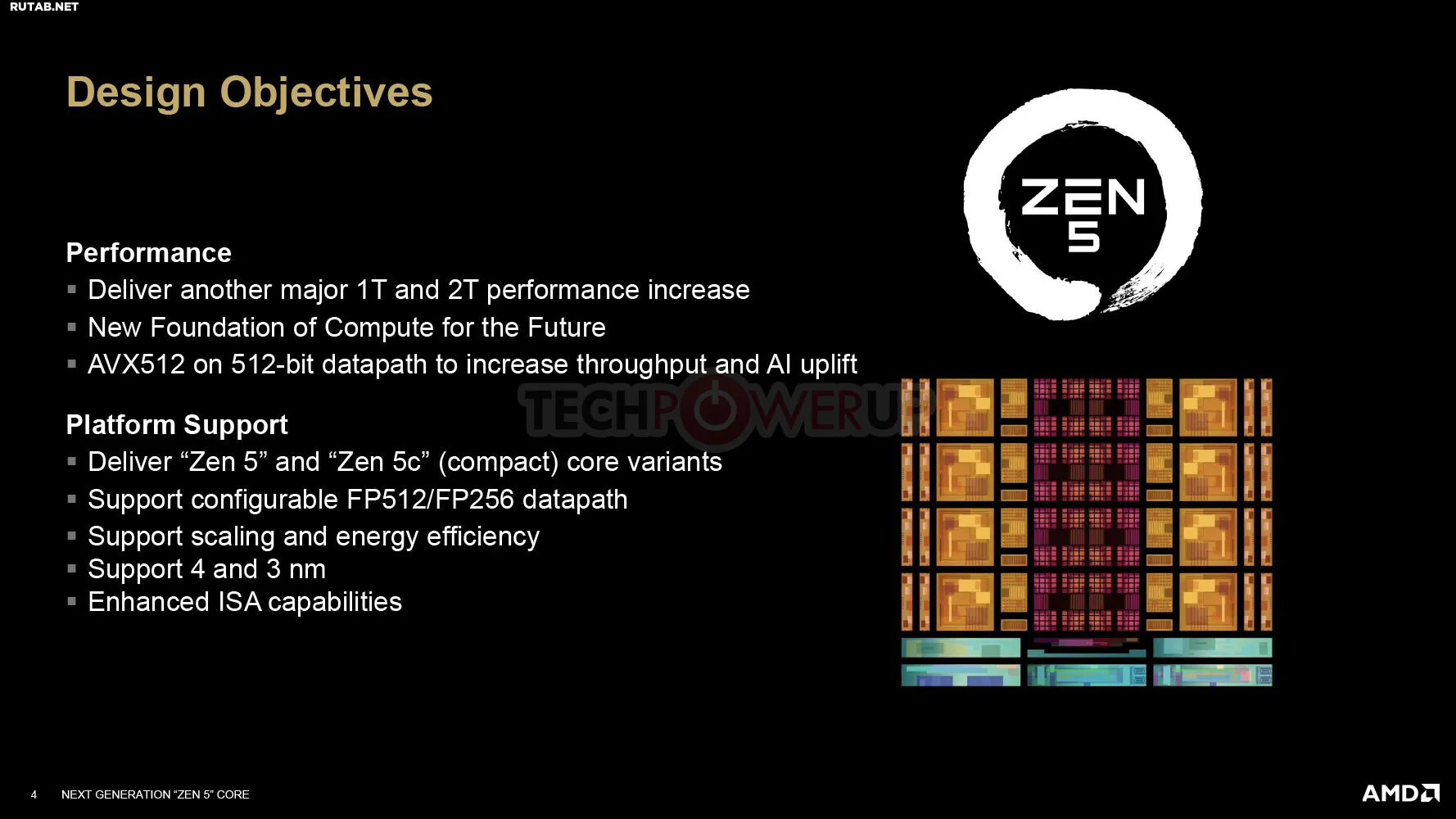

Похоже, что AMD не отключила физически доступную функцию, а, скорее, компания разработала варианты ядер «Zen 5» и «Zen 5c», в которых физически отсутствуют 512-битные пути передачи данных. «И вы получаете преимущество в площади, чтобы иметь возможность еще немного масштабироваться», — продолжил Кларк. Это говорит о том, что ядра Zen 5 и Zen 5c в Strix Point физически меньше, чем ядра 4-нм 8-ядерной CCD Eldora, которая используется в Granite Ridge и некоторых ключевых моделях. будущих серверных процессоров EPYC «Turin» 5-го поколения.

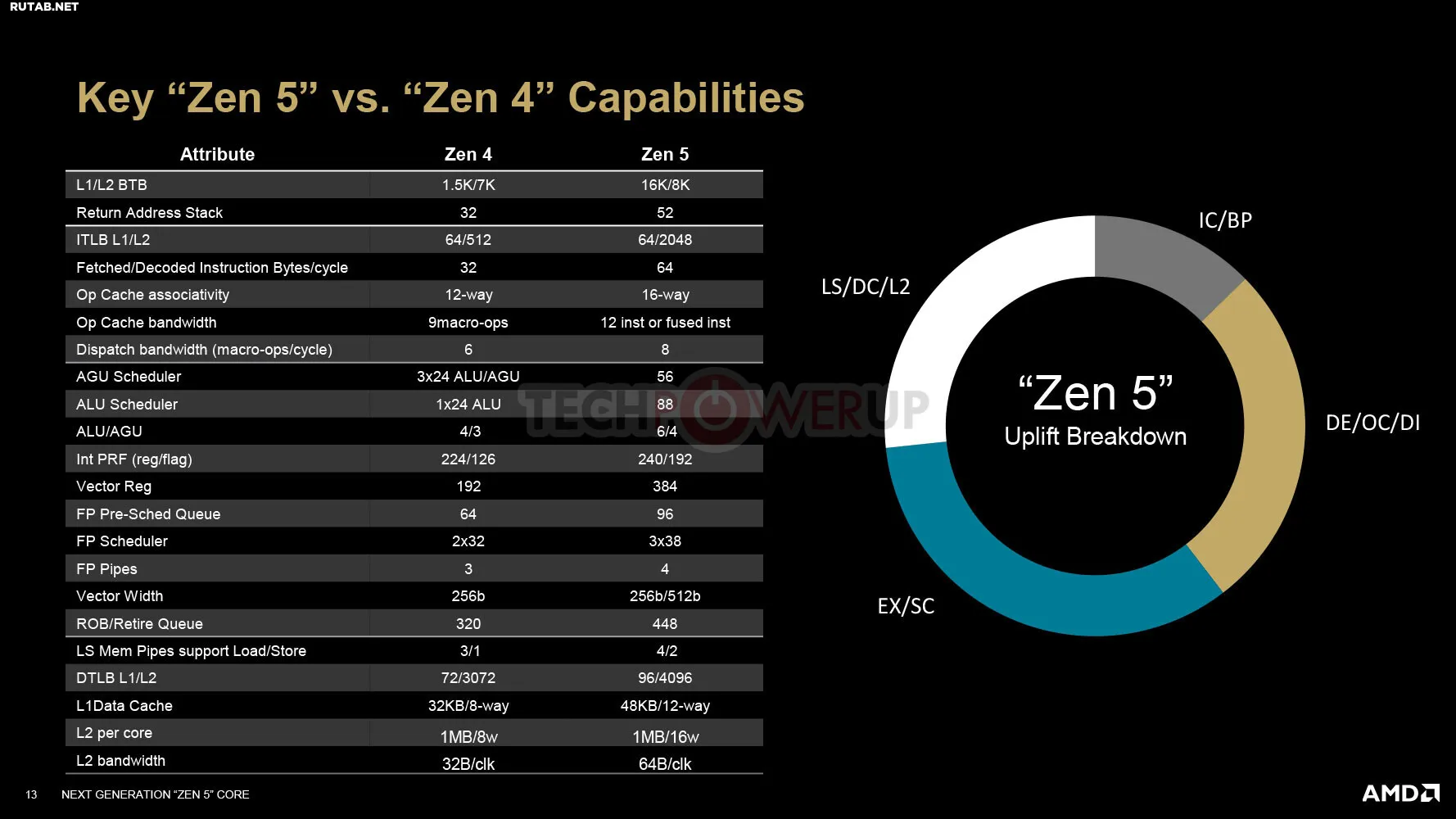

Одной из главных достопримечательностей микроархитектуры «Zen 5» является ее модуль вычислений с плавающей запятой, который поддерживает AVX512 с полным 512-битным каналом передачи данных. Для сравнения, Zen 4 предыдущего поколения обрабатывал AVX512 с использованием 256-битного FPU с двойной накачкой. Новый 512-битный FPU, в зависимости от конкретной рабочей нагрузки и других факторов, примерно на 20–40 % быстрее, чем Zen 4 при 512-битных рабочих нагрузках с плавающей запятой, поэтому ожидается, что Zen 5 продемонстрирует значительный прирост. в оценке производительности искусственного интеллекта, а также в тестах, использующих AVX512.

Мы не уверены, как отсутствие 512-битного пути данных FP влияет на производительность инструкций, связанных с ускорением искусственного интеллекта, поскольку «Strix Point» в основном разрабатывается для ПК с искусственным интеллектом, готовых к Microsoft Copilot+. Вполне возможно, что AVX512 и AVX-VNNI работают на 256-битном канале данных с двойной накачкой, аналогично тому, как это делается в «Zen 4». Такой подход может дать некоторые преимущества в производительности/Ваттах, что может иметь отношение к мобильным платформам.

Источник: Techpowerup.com

0 комментариев