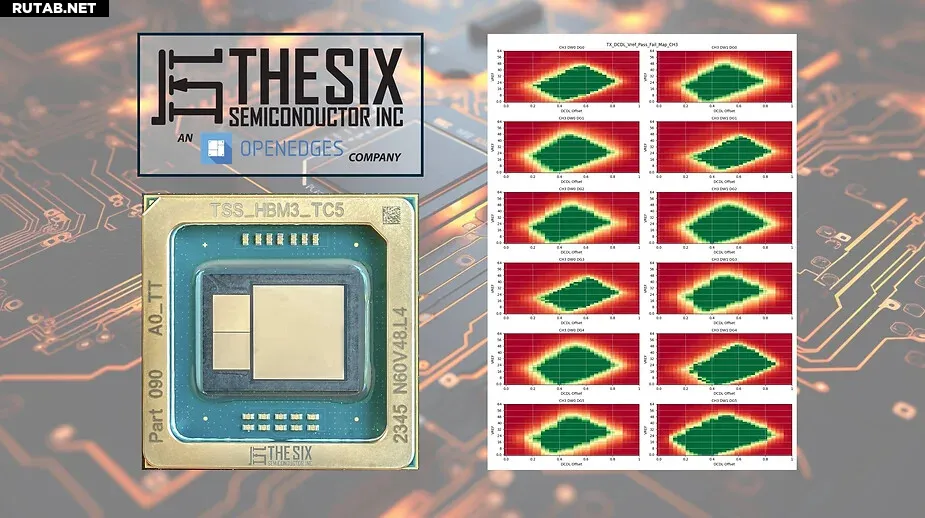

OPENEDGES успешно протестировала свой 7-нм тестовый чип HBM3

OPENEDGES Technology, Inc, ведущий поставщик IP-подсистем памяти, рада сообщить, что ее дочерняя компания The Six Semiconductor Inc (TSS) успешно представила и проверила свой тестовый чип HBM3 по 7-нм техпроцессу. Тестовый чип проверки IP и PHY HBM3 были доведены в течение первого месяца до 6,4 Гбит/с, а дальнейшая настройка привела к успешной работе подсистемы памяти HBM3, разогнанной до 7,2 Гбит/с.

На сегодняшний день лишь несколько поставщиков IP-продукции реализовали и продемонстрировали подсистемы памяти HBM3, поскольку доступность тестовых шаттлов и образцов стека кристаллов HBM3 DRAM сильно ограничена. OPENEDGES рада быть одной из немногих компаний, продемонстрировавших подсистему памяти HBM3 в кремниевом исполнении.

«Наша уверенность в возможностях нашей опытной команды инженеров позволила нам взяться за чрезвычайно сложную разработку HBM3 PHY IP и тестового чипа. Мы очень рады продемонстрировать свое мастерство, плавно и успешно внедрив наш тестовый чип HBM3». — сказал Фархад Хагиги Заде, главный инженер TSS и руководитель проекта HBM3 PHY и тестового чипа.

HBM3 PHY использует современную архитектуру для максимизации запасов по времени и напряжению при изменениях процесса, напряжения и температуры, одновременно сводя к минимуму прерывания трафика данных. HBM3 PHY IP имеет возможность поддерживать до 16 независимых асинхронных каналов, каждый из которых имеет 2x32-битных псевдоканала DWORD.

Дополнительные функции включают в себя быстрое переключение частоты (множественные заданные значения частоты), обработку переходных ошибок (например, ECC, четность данных и сигналов команд/адресов), а также восстановление полос (переназначение резервирования межсоединений), которое автоматически обнаруживает, исправляет и перераспределяет случае проблем с межсоединениями, делая их прозрачными для контроллера памяти.

Разработка подсистемы памяти HBM3 существенно отличается от разработки других традиционных вариантов DDR, поскольку контроллер памяти/PHY SoC находится в 2.5D-интеграции вместе со стеком кристаллов HBM3, кремниевым интерпозером и подложкой корпуса. Требуется высокая степень согласованности физической архитектуры, чтобы десятки тысяч микровыступов SoC были назначены, подключены и проверены правильно. По существу, для тщательного управления переплетенными зависимостями на нескольких уровнях иерархии проектирования требуется сложный дизайн физических конструкций. Например, назначение массива микровыступов повлияет на план PHY на уровне чипа, а также на маршрутизацию RDL на кремниевом интерпозере. Вдобавок ко всему, существует постоянная потребность в надежной вертикальной подаче энергии и заземления среди моря сигналов; то, что требует предварительного планирования (наряду с высокоскоростной маршрутизацией сигналов), а не второстепенной мысли.

Методология, использованная при разработке тестового чипа HBM3 PHY, очень хорошо подходит для будущих проектов чиплетов. От раннего физического планирования маршрутизации сигналов и подачи питания/земли до совместного планирования выступов и шариков BGA вместе с маршрутами и плоскостями подложки корпуса, до необходимой физической проверки и перекрестных проверок; это лишь часть опыта и практических ноу-хау, необходимых при планировании и разработке усовершенствованного чиплета подсистемы памяти.

Благодаря доказанному успеху HBM3 PHY и тестовому чипу, проверенной методологии и опыту проектирования, а также полному портфолио IP-адресов подсистем памяти, OPENEDGES позиционируется как предпочтительный поставщик IP-адресов подсистем памяти для чиплетов.

«Мы очень гордимся успешным внедрением и потрясающими результатами нашего тестового чипа HBM3, демонстрирующим не только нашу способность реализовывать проекты, но также запускать и настраивать подсистему памяти для максимизации производительности», — сказал Ричард Фунг, генеральный директор компании ТСС. «Благодаря философии разработки продуктов, направленной на внедрение новейших технологий DDR в зрелые технологические узлы, наша линейка усовершенствованных IP-адресов подсистемы памяти идеально подходит для всех, кто хочет создать чиплет ввода-вывода с интерфейсами памяти. Наши контроллеры памяти и PHY полностью интегрированы, полностью интегрированы. проверено и готово к использованию в чипсетах наших клиентов».

«Успешная проверка нашего тестового чипа HBM3 — это не просто важная веха, но и свидетельство ценности нашей технологии», — сказал Шон Ли, генеральный директор OPENEDGES Technology. «Мы продолжаем добиваться значительного прогресса в проверке наших IP-адресов на передовых узлах, предпринимая дальнейшие шаги, чтобы предоставить нашим партнерам превосходную производительность и надежность».

Источник: OPENEDGES

0 комментариев