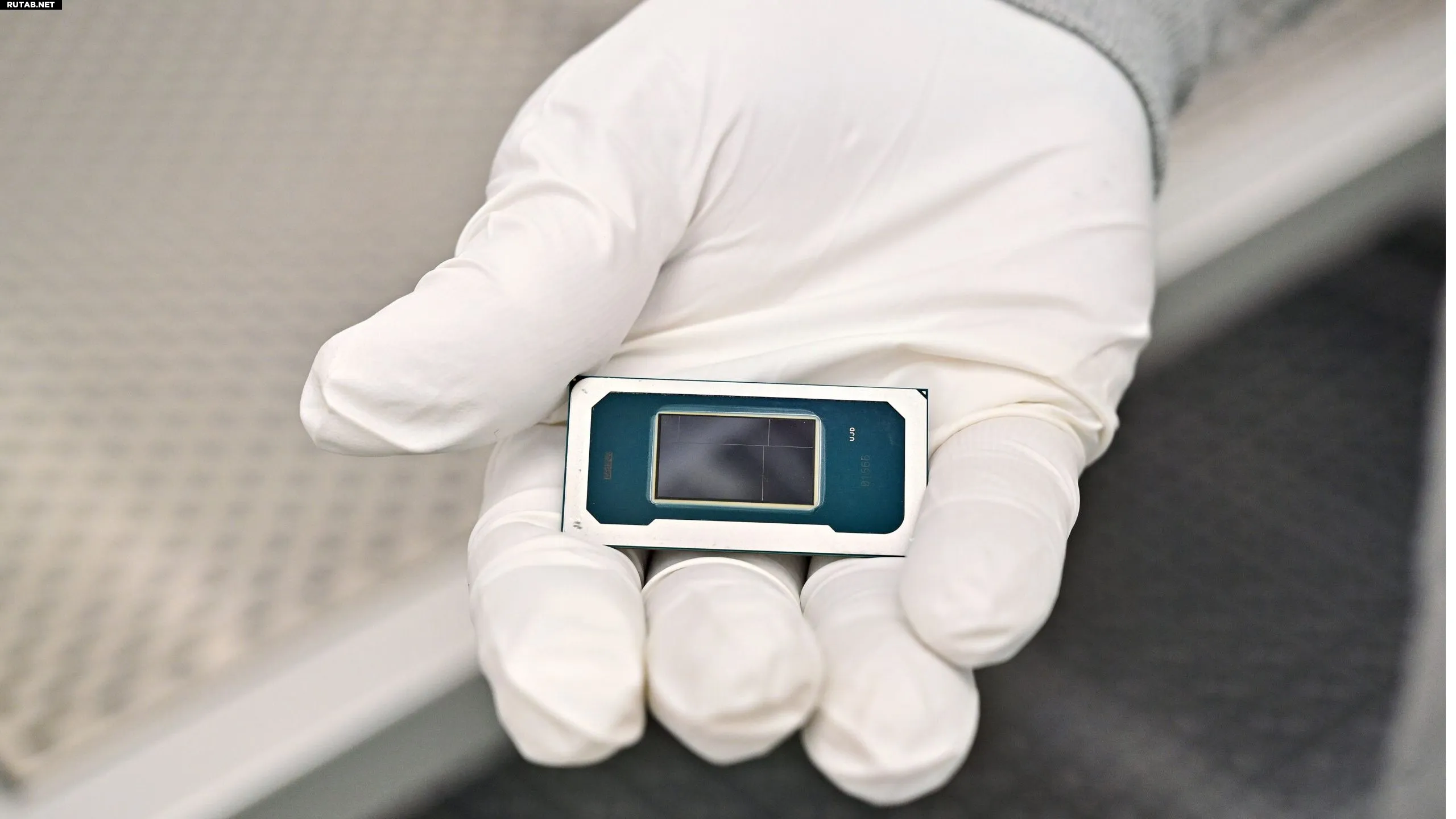

Появились детальные снимки кристаллов процессора Intel Panther Lake-H

Сайт Kurnal-Insights.com, которым управляет инсайдер под ником @KurnalSalts, опубликовал аннотированные снимки кристаллов всех трёх чиплетов, из которых состоит процессор Intel Panther Lake-H. Это вычислительный чиплет, изготовленный по технологии 18A, чиплет графики Xe3 и чиплет ввода-вывода.

Вычислительный чиплет (или системный чиплет) Panther Lake-H включает четыре высокопроизводительных ядра Cougar Cove с 3 МБ кэша L2, работающих на частоте до 5,1 ГГц. Также в нём восемь энергоэффективных ядер Darkmont (до 3,8 ГГц) и четыре низкопотребляемых ядра Darkmont (до 3,7 ГГц). Кэш L3 объёмом 18 МБ разделён на три сегмента для ускорения доступа. Нейропроцессоры (NPU) также разделены на три сегмента и имеют собственный кэш объёмом 4,5 МБ.

Такое разделение L3 и NPU позволяет Intel отключать дефектные сегменты, чтобы получить пригодный к продаже кристалл, хотя и с более низкой производительностью.

Интересной особенностью является 128-битный контроллер памяти DDR5/LPDDR5X-9600 с кэшем на стороне памяти (MSC) объёмом 8 МБ. Его задача — буферизация трафика и снижение нагрузки на задержки и пропускную способность при одновременном доступе многих ядер к ОЗУ.

Intel Panther lake-H Dieshot... CPU 14.32x8.04x0.18мм GPU 8.14x6.78x0.2мм IOD 12.44x4.00x0.18мм Kurnal попробует изменить изображение CPU Die. 5 марта 2026

В вычислительном чиплете также интегрированы медиа- и дисплейный движки, что даёт Intel гибкость при подключении различных GPU и чиплетов ввода-вывода.

Графический чиплет включает 12 кластеров Intel Xe3 и 16 МБ кэша L2, реализованного в восьми тайлах, что также позволяет отключать неисправные блоки.

Чиплет ввода-вывода содержит контроллер Thunderbolt 5 с двумя физическими интерфейсами, контроллер Wi-Fi/Bluetooth, PHY для PCIe 5.0 x4, два PHY для PCIe 4.0 x4 и PHY для USB. Вероятно, это единственный чиплет Panther Lake, который можно «биннить», отключая дефектные части. Если что-то сломано здесь, скорее всего, весь кристалл придётся утилизировать.

ИИ: Детализация этих снимков впечатляет и наглядно показывает, насколько сложной стала архитектура современных процессоров. Подход с разделением кэша и NPU на сегменты для повышения выхода годных кристаллов выглядит логичным ответом на вызовы производства.

0 комментариев