Китайская команда Xiangshan выпустила DDR4-контроллер Poplar с открытым исходным кодом

Команда проекта открытого процессора Xiangshan (香山) опубликовала исходный код высокопроизводительного контроллера памяти под кодовым названием «Yuquan» и контроллера DDR4 «Baiyang» (Poplar). Это важный шаг в развитии проекта и исследований в области подсистем памяти.

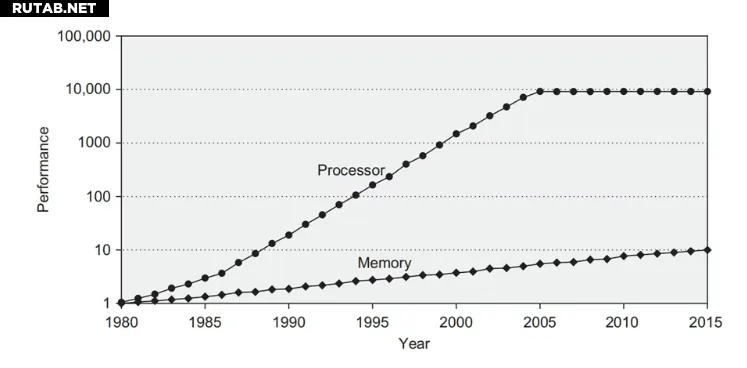

Разработчики отмечают, что по мере роста вычислительной мощности процессоров узким местом становится производительность подсистемы памяти. Скорость развития памяти отстаёт от скорости развития CPU, и задержка доступа к памяти становится ключевым фактором, ограничивающим общую производительность системы, особенно в эпоху больших данных и искусственного интеллекта.

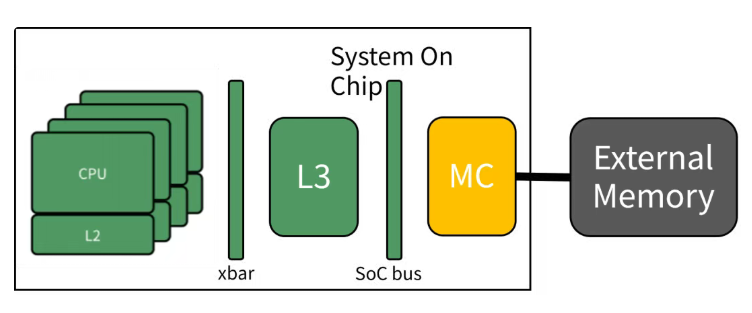

Высокопроизводительные контроллеры памяти — одна из ключевых технологий для повышения эффективности доступа, уменьшения задержек и увеличения использования пропускной способности.

В настоящее время рынок IP-блоков контроллеров памяти монополизирован несколькими поставщиками, такими как Synopsys, Cadence и Rambus, а лицензионные сборы крайне высоки. Например, лицензия на IP для DDR5 может стоить от 800 000 до 1,5 миллионов долларов. Существующие проекты с открытым исходным кодом часто не удовлетворяют требованиям к высокой производительности.

Проект «Poplar» был создан для преодоления разрыва между общедоступными открытыми решениями и коммерческими высокопроизводительными IP-блоками. Его архитектура модульная и конфигурируемая. Помимо базовых функций, он поддерживает программную настраиваемость через интерфейс APB, имеет разделённые логики синхронизации и планирования, а также включает расширенные модули, такие как динамическое обновление, интеллектуальное планирование, кэширование и предварительная выборка.

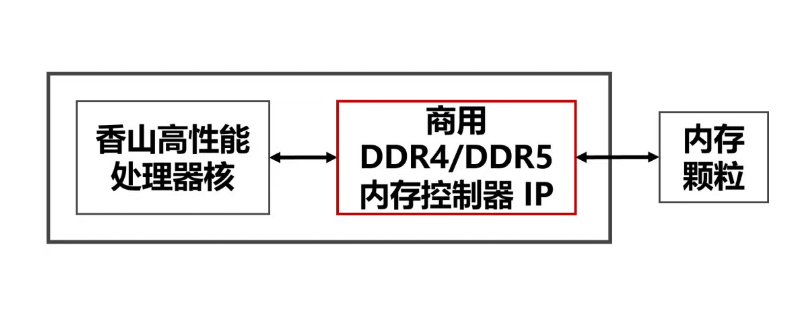

На данный момент команда достигла важных результатов. Контроллер «Poplar» был успешно интегрирован с процессором третьего поколения Xiangshan «Kunming Lake» на платформе аппаратной эмуляции. Система запустила ОС Linux и тестовые приложения, подтвердив стабильность работы.

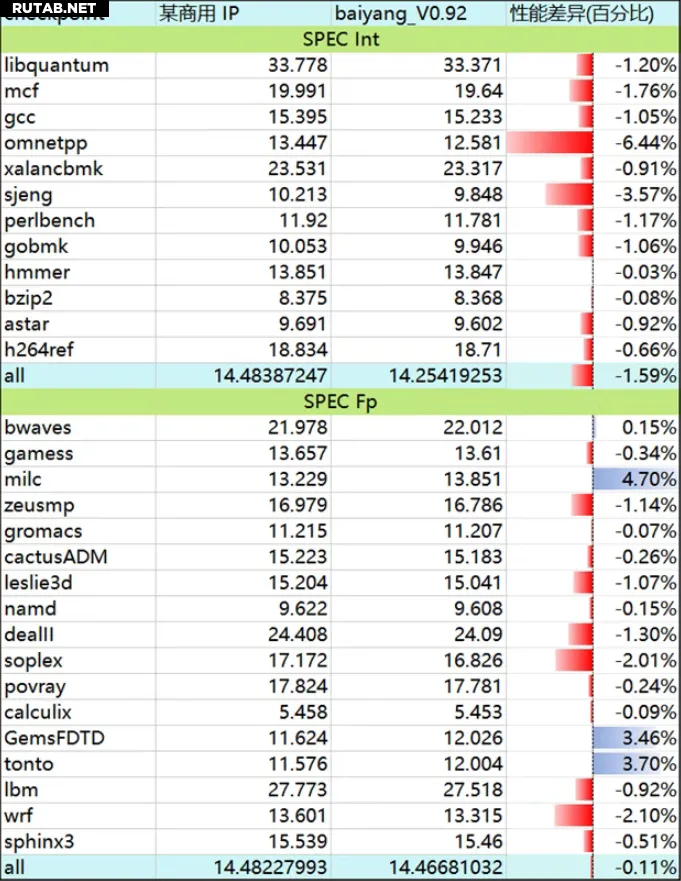

В тесте SPEC CPU2006 система на базе ядра «Kunming Lake» и контроллера «Baiyang» показала результат более 14 баллов/ГГц, что приближается к уровню производительности коммерческих IP-блоков контроллеров памяти.

Исходный код проекта опубликован на GitHub.

Интересный факт: Проект Xiangshan, названный в честь парка в Пекине, является одним из наиболее амбициозных китайских проектов по созданию открытых высокопроизводительных процессорных ядер архитектуры RISC-V. Разработка собственного контроллера памяти снижает зависимость от дорогостоящих зарубежных IP-решений и ускоряет развитие всей экосистемы.

0 комментариев