AMD исследует технологию 3D-стэкинга для L2-кэша

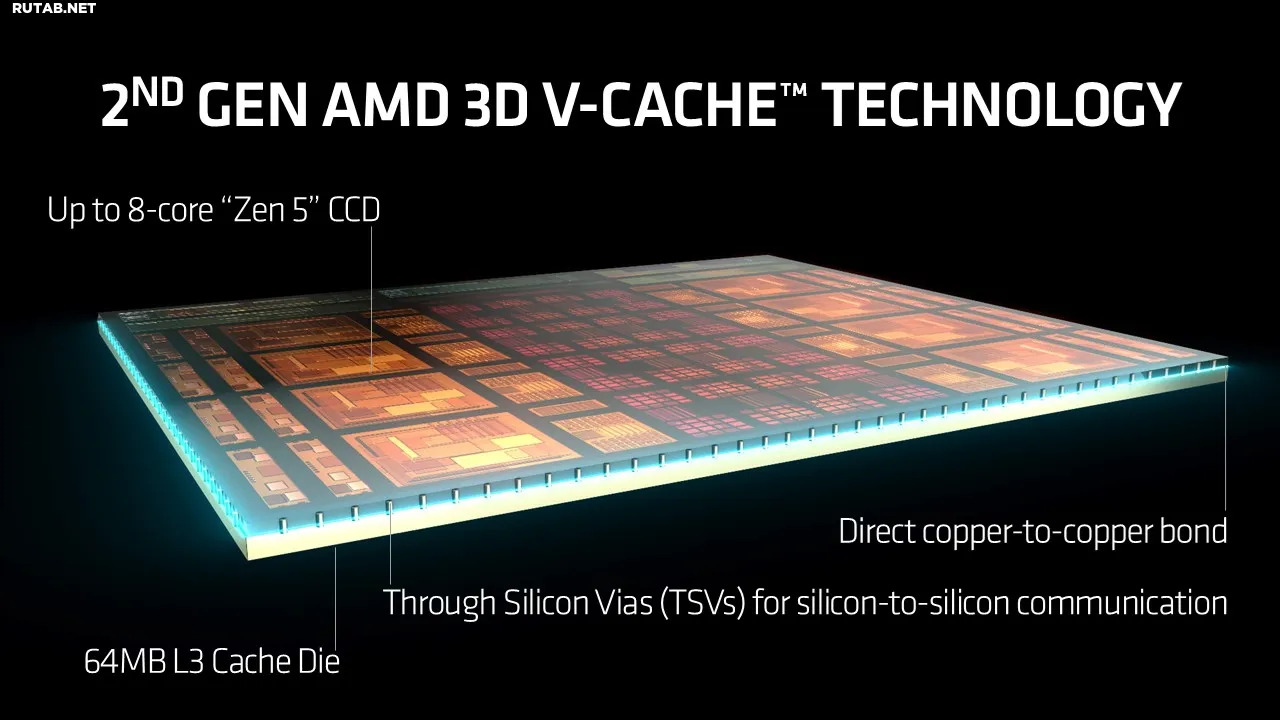

После успеха технологии 3D V-Cache, позволившей AMD доминировать на рынке игровых процессоров за счёт стэкинга L3-кэша, компания не останавливается на достигнутом.

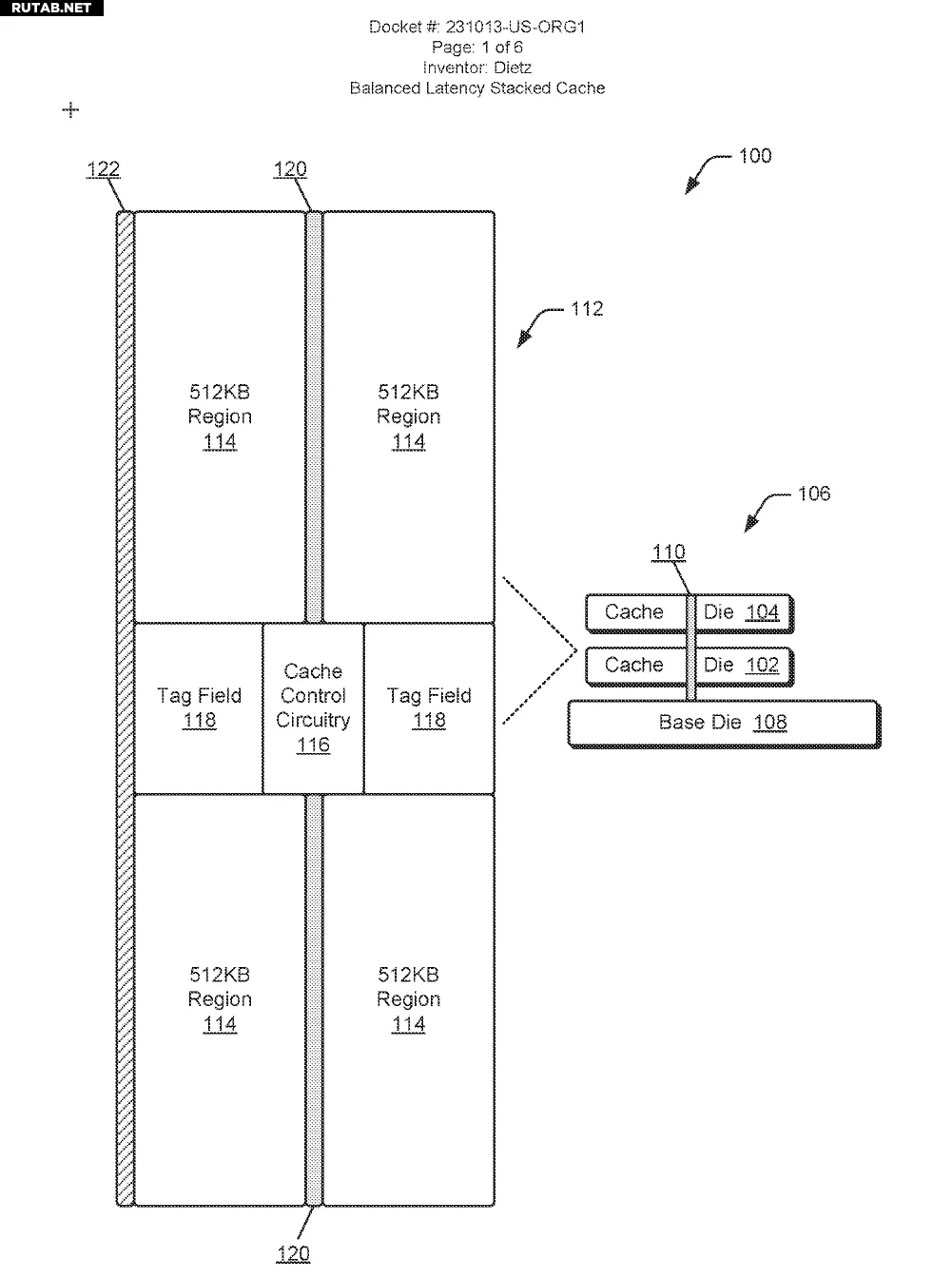

Недавно AMD опубликовала исследовательскую работу под названием «Сбалансированный стэкинг кэша с низкой задержкой» (Balanced Latency Stacked Cache, патент US20260003794A1), раскрывающую следующий шаг в развитии архитектуры кэш-памяти: стэкинг L2-кэша.

В настоящее время 3D V-Cache в основном повышает производительность за счёт добавления дополнительного L3-кэша поверх или под вычислительные ядра. Новый патент показывает, что AMD изучает возможность применения стэкинг-технологии к более быстрому и близкому к ядрам L2-кэшу.

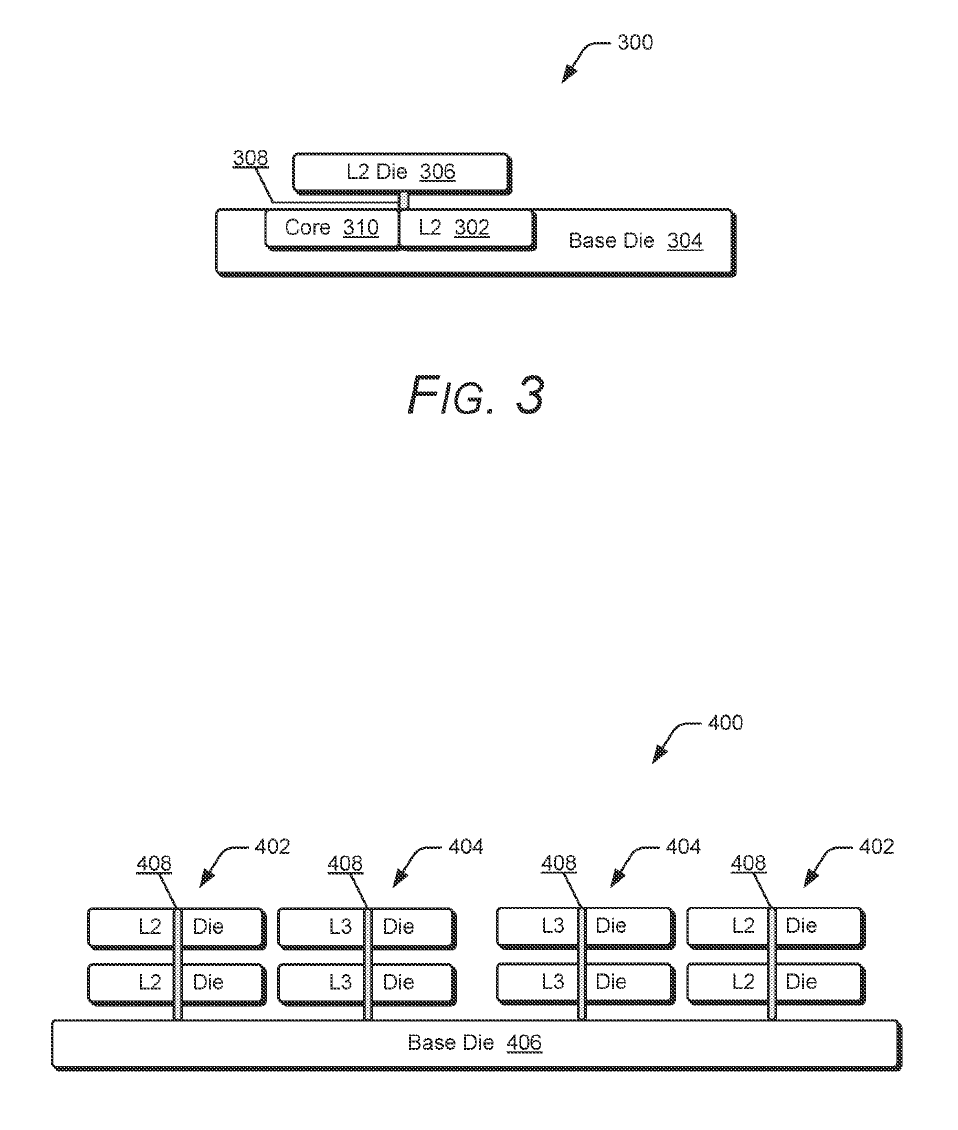

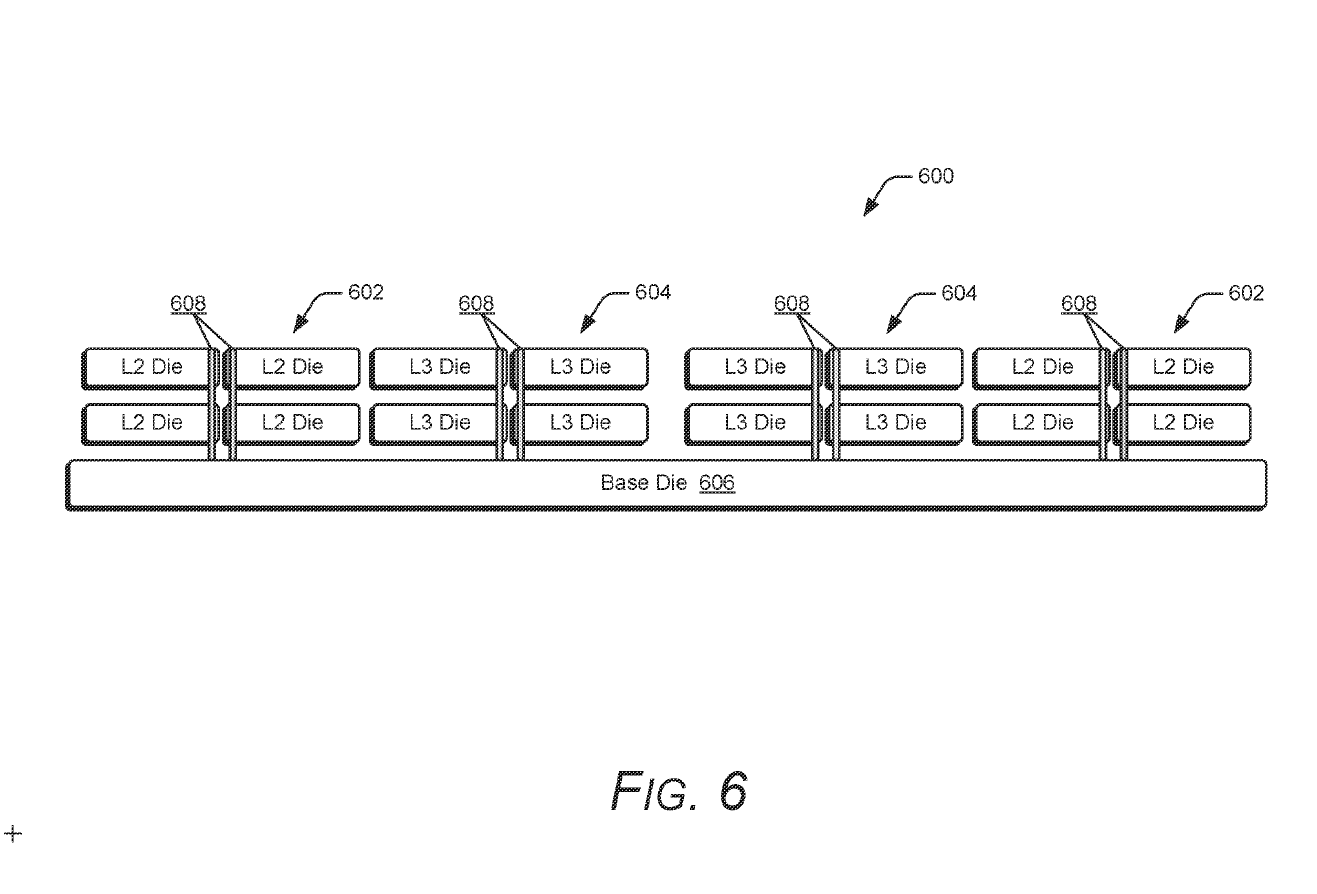

На примере схемы видно, что AMD рассматривает многослойную стэкинг-структуру. Базовый слой соединяет вычислительные ядра с модулями кэша, а поверх него можно наращивать дополнительные слои (кристаллы) кэш-памяти. Например, модуль L2 объёмом 2 МБ, состоящий из четырёх областей по 512 КБ, может быть расширен до 4 МБ.

Метод стэкинга использует те же принципы, что и 3D V-Cache: кремниевые сквозные отверстия (TSV) соединяют стэкированный L2/L3-кэш с базовым кристаллом и вычислительным комплексом. Конфигурация размещается в центре стэкированной кэш-системы по вертикали, а контроллер CCC управляет вводом и выводом данных.

В работе AMD, используя в качестве примера плоские конфигурации L2-кэша объёмом 1 МБ и 2 МБ, указывает, что типичная задержка плоского L2-кэша 1 МБ составляет 14 циклов, в то время как задержка стэкированного L2-кэша 1 МБ — 12 циклов.

Это говорит о том, что стэкированный L2-кэш может не только обеспечить бо́льшую ёмкость, но и достичь схожей или даже лучшей задержки в циклах по сравнению с типичным плоским методом. Кроме того, AMD отмечает, что такая архитектура обладает явными преимуществами в экономии энергопотребления.

0 комментариев