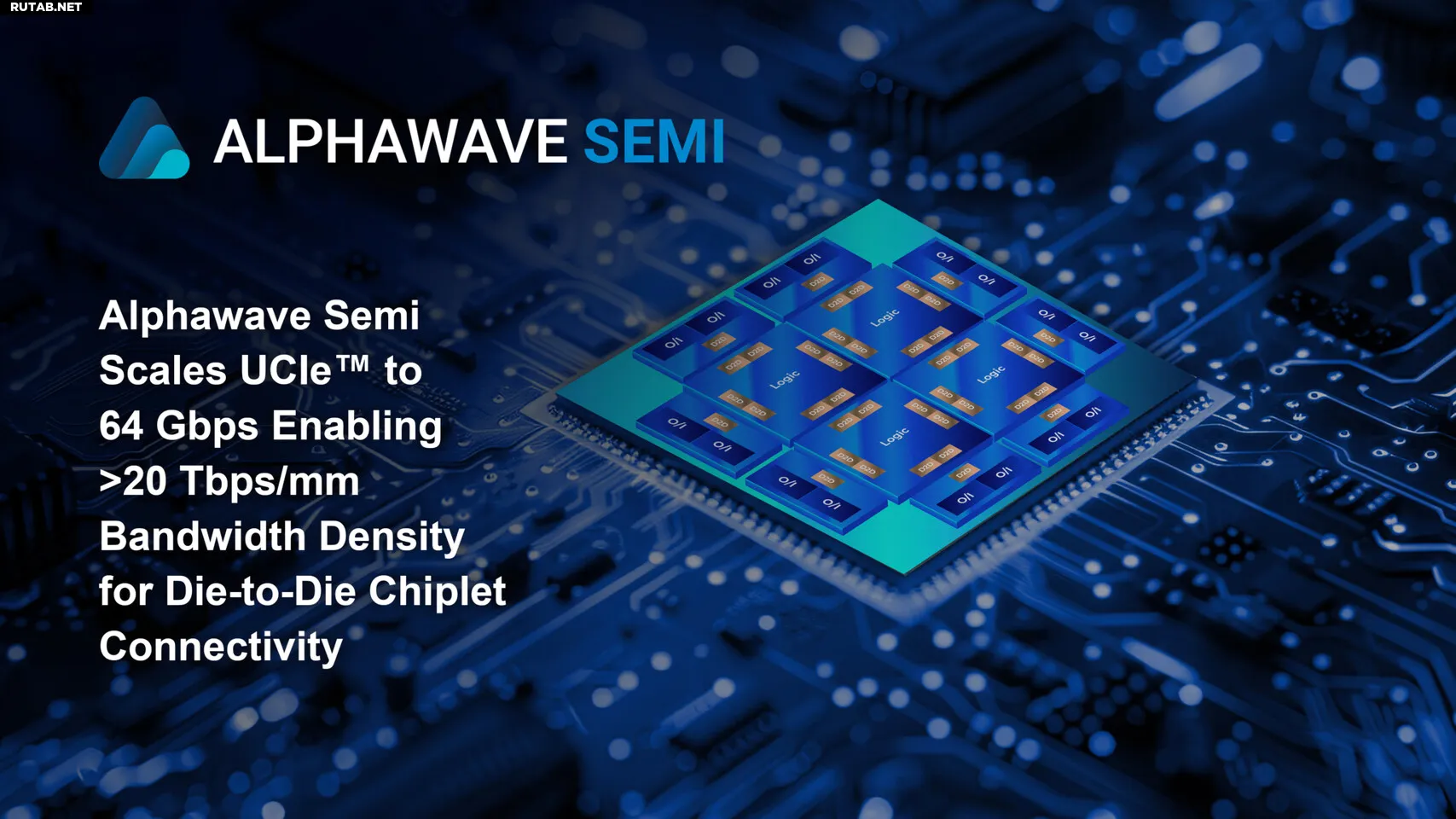

Alphawave Semi масштабирует UCIe до 64 Гбит/с для 3-нм кристалла-кристалла соединения чипов

Техпроцесс 3 нм (англ. 3 nm) — технологический процесс в производстве полупроводниковых приборов. 3-нм процесс является следующей ступенью миниатюризации техпроцесса после 5-нанометрового. По состоянию на 2022 год тайваньский производитель микросхем TSMC планировал запустить в серийное производство 3-нм полупроводниковый узел под названием N3 ко второй половине 2022 года. Википедия

Alphawave Semi собирается произвести революцию в области связи с помощью Gen 3 64 Gbps UCIe IP, обеспечивая плотность полосы пропускания более 20 Tbps/mm, с ультранизким энергопотреблением и задержкой. Это решение имеет высокую степень настройки, поддерживает несколько протоколов, включая AXI-4, AXI-S, CXS, CHI и CHI-C2C, чтобы удовлетворить растущие потребности в высокопроизводительном подключении в дезагрегированных системах в высокопроизводительных вычислениях (HPC), центрах обработки данных и приложениях искусственного интеллекта (AI).

Проект соответствует новейшей спецификации UCIe и имеет масштабируемую архитектуру с функциями расширенной тестируемости, включая мониторинг работоспособности каждой дорожки в режиме реального времени, что делает его надежной основой и позволяет создать открытую и совместимую экосистему чиплетов.

Межсоединения UCIe D2D облегчают ряд стандартных и новых сценариев подключения чиплетов. Обычные применения включают связывание вычислительных чиплетов для малозадерживаемого, когерентного соединения через потоковые возможности UCIe, а также подключение вычислений к чиплетам ввода-вывода с использованием интерфейсов UCIe с PCIe, CXL или Ethernet. Кроме того, оптические ретаймеры могут использовать архитектуру чиплетов UCIe для установления надежных оптических каналов ввода-вывода с малозадерживаемым через оптические двигатели, улучшая внесистемное подключение. Это поддерживает разработку маломощных, высокоскоростных решений в центрах обработки данных и системах AI/ML.

Для высокопроизводительных приложений создание собственного базового кристалла HBM с использованием новейшего стандарта UCIe является передовым подходом, который включает в себя тесную интеграцию кристаллов памяти с вычислительными кристаллами для достижения чрезвычайно высокой пропускной способности, а также низкой задержки между компонентами. Это позволяет повторно использовать береговую линию между кристаллами, уже занятую на основном кристалле, для соединений ядро-ядро или ядро-ввод-вывод. Этот подход значительно оптимизирует транзакции памяти в приложениях ИИ, где низкое энергопотребление и уменьшенная задержка являются отличительными чертами производительности.

«UCIe Consortium рад видеть, что его участники достигают таких важных вех, как тейпауты, которые демонстрируют растущее принятие спецификации UCIe», — сказал Брайан Ри, председатель рабочей группы по маркетингу UCIe Consortium. «UCIe является краеугольным камнем индустрии чиплетов, предоставляя надежное решение для высокоскоростных межсоединений между кристаллами с низкой задержкой. Принимая открытые стандарты, мы даем возможность отрасли ускорить инновации, сократить время выхода на рынок и предоставить новаторские технологии.Это достижение, наряду с более ранней разработкой Alphawave Semi — первым в отрасли 3-нм проверенным кремниевым процессором Gen1 UCIe IP, подтверждает стремительный прогресс компании как лидера в области высокопроизводительных решений для подключения чиплетов с полным набором проверенных кремниевым процессором IP-подсистем подключения, специально разработанных для рынков гипермасштабируемых решений и инфраструктуры данных.«Наш успешный выпуск Gen 2 UCIe IP на скорости 36 Гбит/с на 3 нм технологии основан на нашем новаторском проверенном кремнием 3 нм UCIe IP с упаковкой CoWoS», — сказал Мохит Гупта, старший вице-президент и генеральный менеджер по заказным кремниям и IP, Alphawave Semi. «Это достижение закладывает основу для нашего Gen 3 UCIe IP на скорости 64 Гбит/с, который нацелен на обеспечение высокой производительности, пропускной способности 20 Тбит/с/мм для наших клиентов, которым требуется максимизация плотности береговой линии для критических потребностей в пропускной способности ИИ в 2025 году».

Источник: Alphawave Semi

0 комментариев