Спецификации UCIe 2.0 стандартизируют архитектуру управления и 3D-упаковку для различных чипсетов

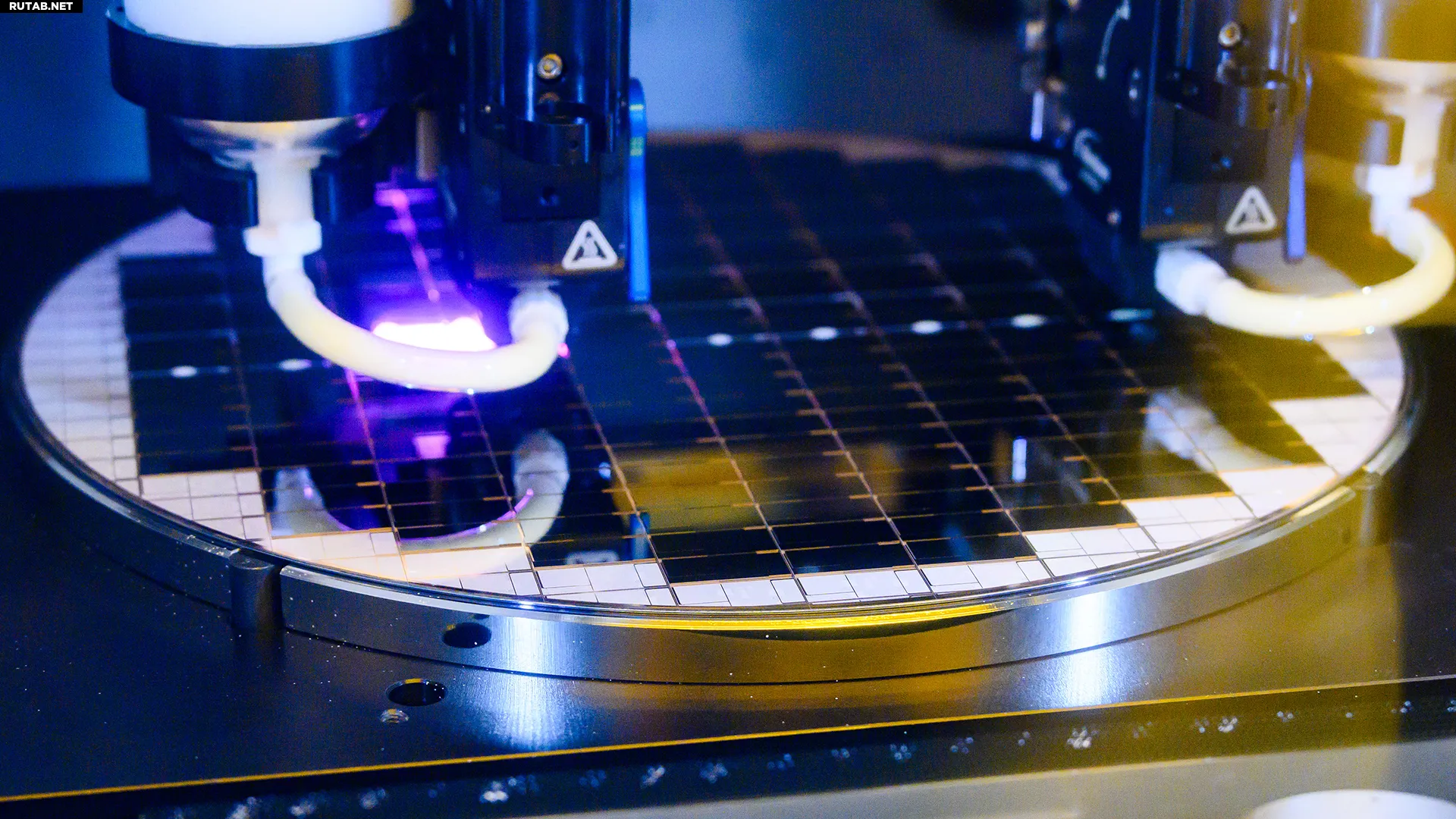

Консорциум UCIe в среду выпустил версию 2.0 спецификации UCIe, которая обеспечивает поддержку стандартизированного управления системной архитектурой различных чиплетов и поддержку стандартной 3D-упаковки чиплетов с гибридным соединением и выступами различных размеров. Новая спецификация упрощает разработку, сборку и управление «системой в пакете» (SiP), содержащей чиплеты от разных производителей.

На данный момент SiP с чипсетами UCIe должны использовать несколько инфраструктур управления для каждого чиплета, если они используют чиплеты от более чем одного поставщика. Спецификация UCIe 2.0 представляет стандартизированную архитектуру системы управления, которая обеспечивает управляемость, возможность тестирования и отладку (Dfx) для нескольких микросхем на протяжении всего жизненного цикла SiP. Кроме того, новая спецификация определяет дополнительную архитектуру UCIe DFx (UDA), которая объединяет независимое от поставщика тестирование, телеметрию и структуру отладки в каждом чиплете, чтобы упростить разработку и внедрение многокристальной системы в корпусах.

Еще одна ключевая особенность UCIe 2.0 — поддержка 3D-упаковки. UCIe-3D оптимизирован для гибридного склеивания, поддерживая неровности размером 1 микрон или меньше (10–25 микрон), чтобы обеспечить гибкость и масштабируемость. Чтобы представить эти цифры в контексте: технология Intel Foveros 3D имеет шаг выступов 36 микрон, поддерживает до 770 микровыступов на квадратный миллиметр и пропускную способность 160 ГБ/с на мм. Будущие усовершенствования будут включать микровыступы толщиной 25 и 18 микрон, что значительно увеличит плотность межсоединений. UCIe-3D будет поддерживать плотность, значительно превышающую ту, которую в настоящее время предусматривают производители микросхем; спецификация предназначена для долгосрочного использования.

Наконец, спецификация UCIe 2.0 включает оптимизированные конструкции пакетов для обеспечения совместимости и эффективного тестирования на соответствие. Целью тестирования на соответствие является проверка поддерживаемых основной полосой частот тестируемого устройства (DUT) на соответствие заведомо исправной эталонной реализации UCIe. Эта спецификация устанавливает начальную основу для тестирования физических компонентов, адаптеров и протоколов.

«Консорциум UCIe поддерживает широкий спектр микросхем для удовлетворения потребностей быстро меняющейся полупроводниковой промышленности», — сказал Чолмин Парк, президент консорциума UCIe и корпоративный вице-президент Samsung. «Спецификация UCIe 2.0 основана на предыдущих итерациях путем разработки комплексного стека решений и поощрения взаимодействия между решениями на чиплетах. Это еще один пример приверженности Консорциума процветающей экосистеме открытых чиплетов».

Источник: Tomshardware.com

0 комментариев