Инженер создает графический процессор с нуля за две недели

Инженер поделился своим опытом «создания графического процессора с нуля, не имея предварительного опыта». Как и в случае с его предыдущим проектом по разработке процессора с нуля, Адаму Маймудару потребовалось всего две недели, чтобы совершить этот умственный подвиг. В ветке Twitter/X Маймудар шаг за шагом рассказывает нам об этом процессе и признает, что проектирование графического процессора оказалось гораздо более сложной задачей, чем ожидалось. Чтобы внести ясность, текущим результатом проекта является макет микросхемы в Verilog, который, наконец, был пропущен через программное обеспечение OpenLane EDA для его проверки. Тем не менее, графический процессор будет отправлен на ленту через Tiny Tapeout 7, поэтому в ближайшие месяцы ему суждено стать физическим чипом.

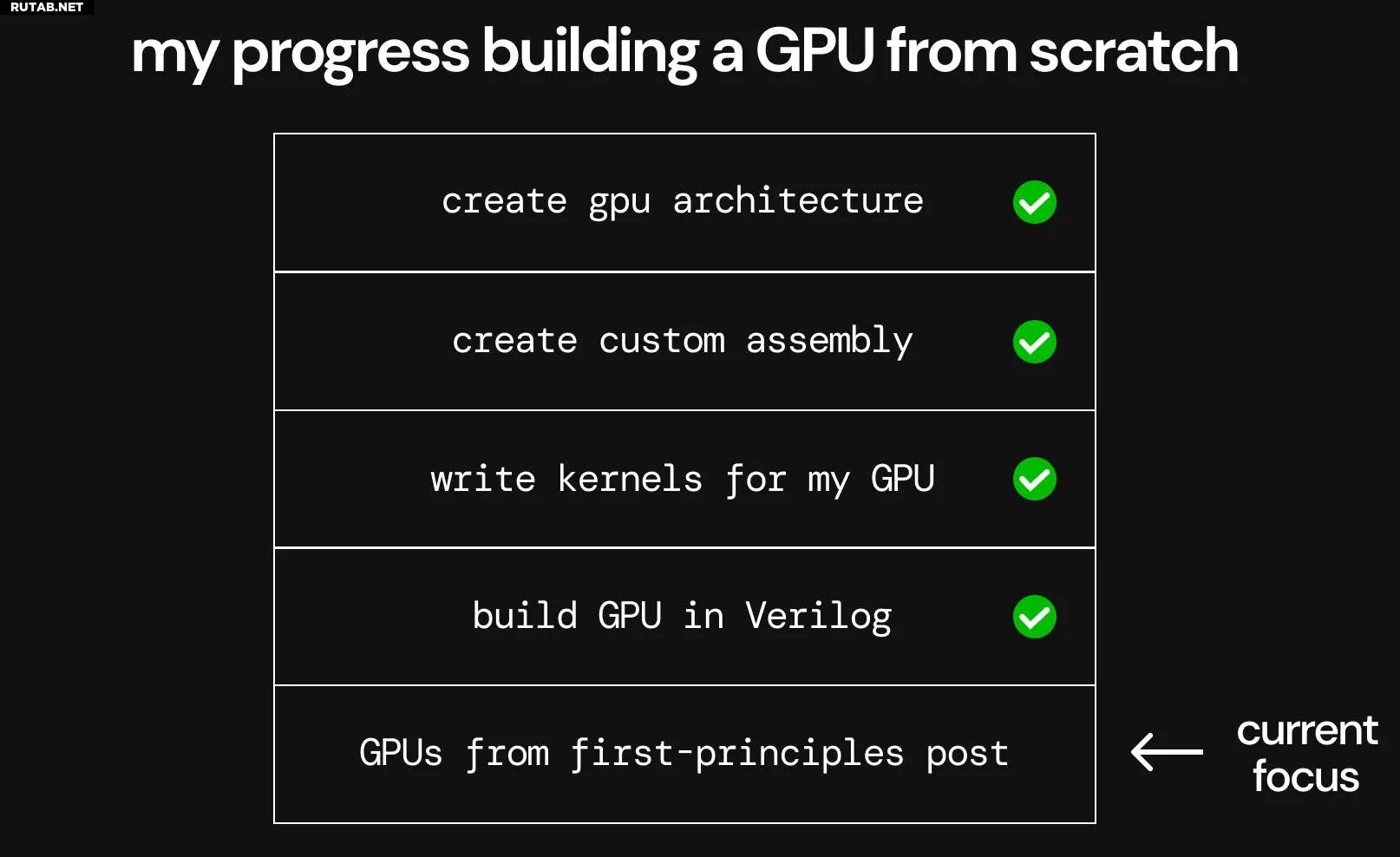

Выше вы можете увидеть последовательность задач, над которыми работал Маджмудар при разработке своего графического процессора. Тем не менее, поскольку проект создавался «с нуля», потребовалось много исследований и размышлений еще до того, как был сделан предварительный шаг. В прошлый раз мы подчеркивали опасения инженера по поводу того, что графические процессоры станут относительно сложной областью исследования из-за доминирования запатентованных технологий, поскольку это предсказание сбылось.

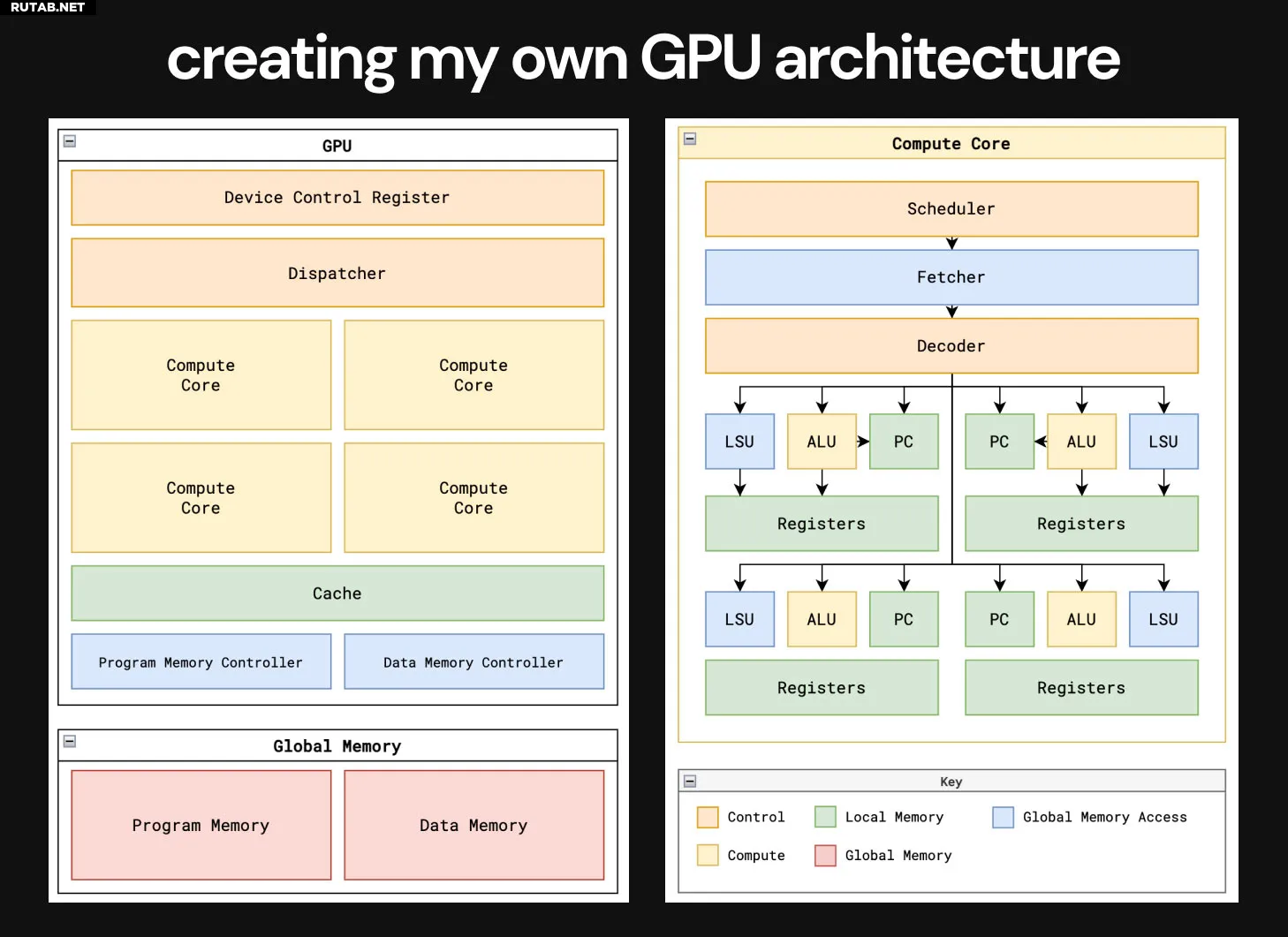

Проведя несколько итераций вышеупомянутой архитектуры, Маймудар решил сосредоточиться на возможностях параллельных вычислений общего назначения (GPGPU). Таким образом, для достижения этой цели он скорректировал свою архитектуру набора команд (ISA), которая содержит всего 11 инструкций. Далее инженер написал два ядра матричных вычислений для работы на своем графическом процессоре. Эти ядра сложения и умножения матриц продемонстрируют ключевые функциональные возможности графического процессора и станут доказательством его полезного применения в задачах графики и машинного обучения.

До сих пор для инженера это было относительно легко, но создание его графического процессора в Verilog представляло «множество проблем». Советы (печально) знаменитого Джорджа Хотца помогли Маджмудару преодолеть одно из первых (и вторых) препятствий, связанных с памятью и реализацией варп-планировщика. Однако третья переписка его кода добилась цели, исправив планирование выполнения вычислительного ядра.

Еще несколько неуказанных изменений позже, а также доказательство пудинга, видео, показывающее работу и проверку ядра сложения матриц, было опубликовано в ветке твитов.

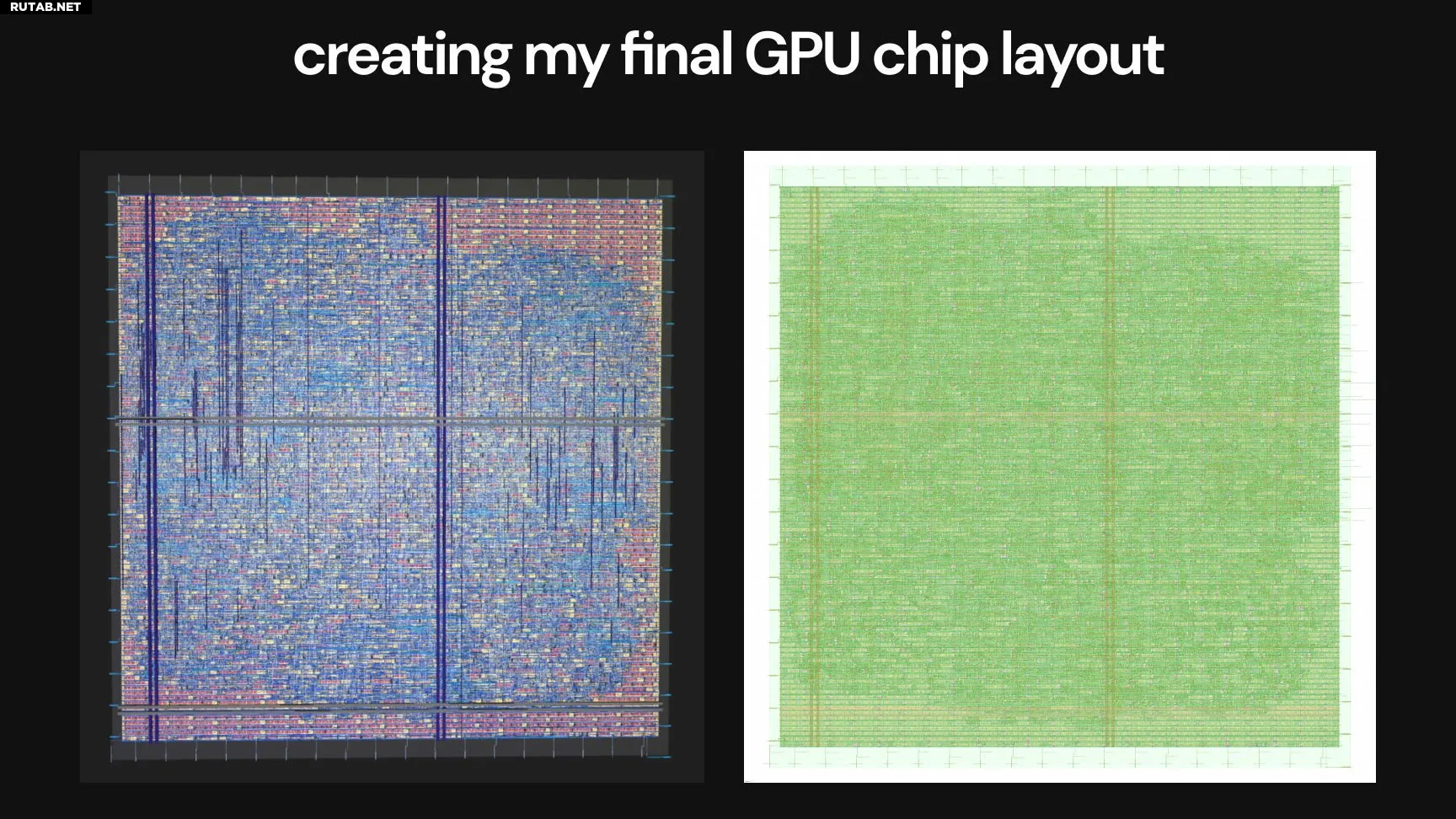

Наконец, завершенный проект Verilog был передан через OpenLane EDA, ориентированный на 130-нм технологический узел Skywater (для Tiny Tapeout). И снова нужно было решить некоторые проблемы. В частности, Маймудар объясняет, что некоторые проверки правил проектирования (DRC) не удались и потребовали переделки.

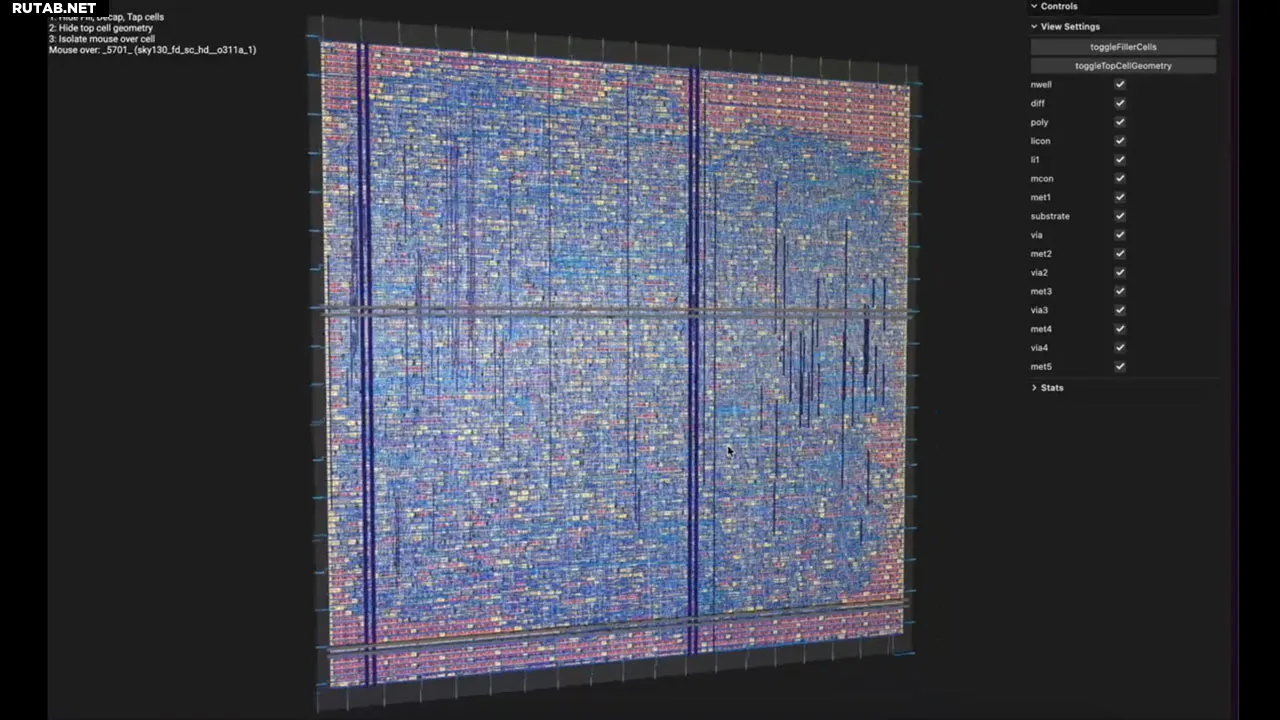

После двухнедельных усилий инженер с удовольствием поигрался с крутой 3D-визуализацией конструкции своего графического процессора. Этого будет достаточно, пока TT7 не вернет кремний участникам. Конечно, эта работа не войдет в число лучших видеокарт. Если вы хотите узнать больше об этом самодельном графическом процессоре, посетите интересную ветку в социальных сетях и/или изучите специальную страницу Tiny-GPU на GitHub.

0 комментариев